# Chapter 6 Combinational CMOS Circuit and Logic Design

#### Jin-Fu Li

Advanced Reliable Systems (ARES) Laboratory Department of Electrical Engineering National Central University Jhongli, Taiwan

### Outline

# Advanced CMOS Logic Design I/O Structures

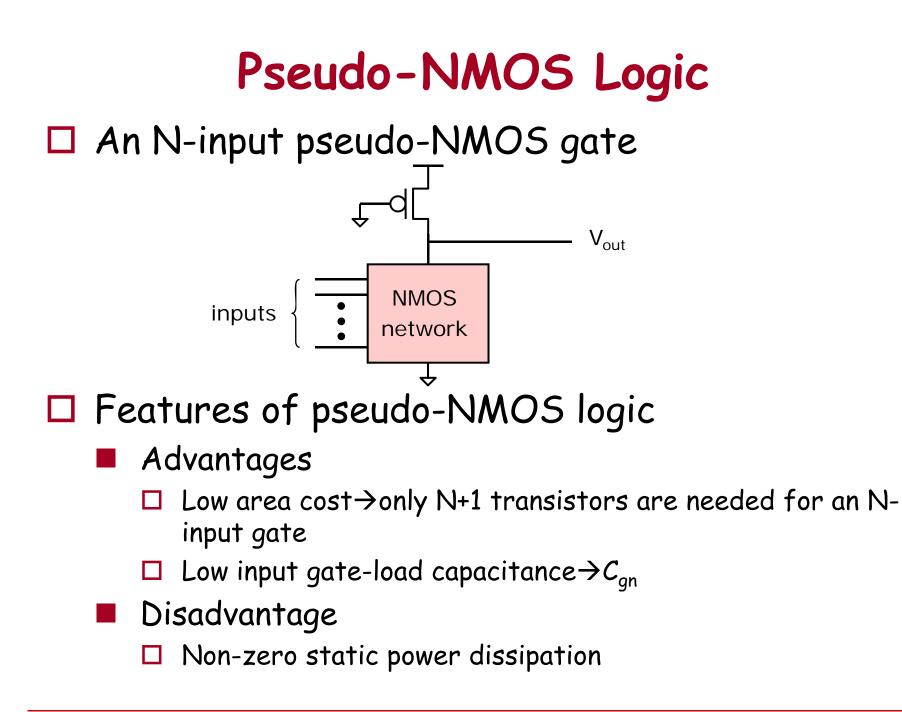

# Pseudo-NMOS Logic

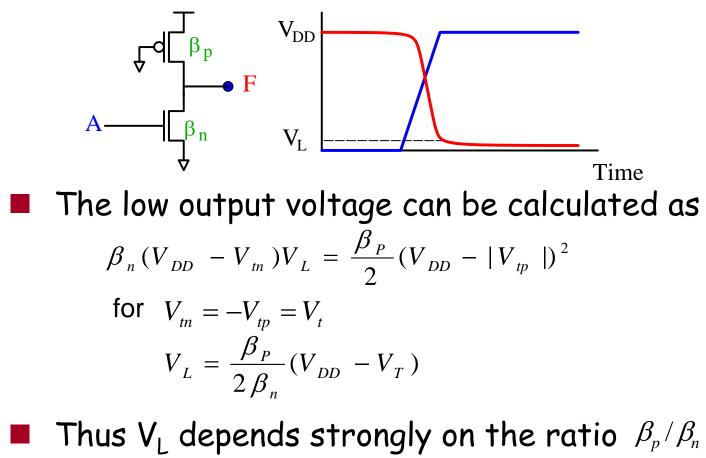

#### □ A pseudo-NMOS inverter

The logic is also called ratioed logic

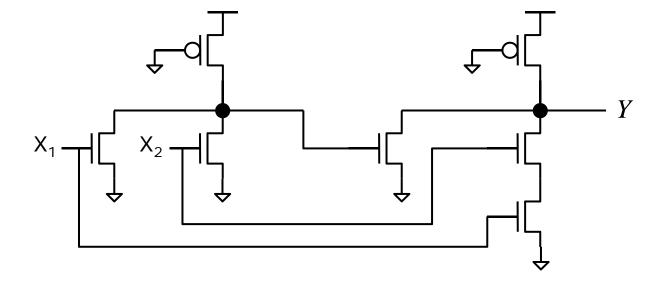

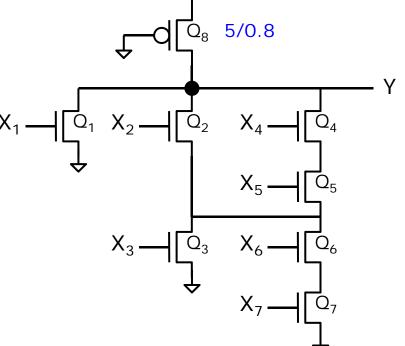

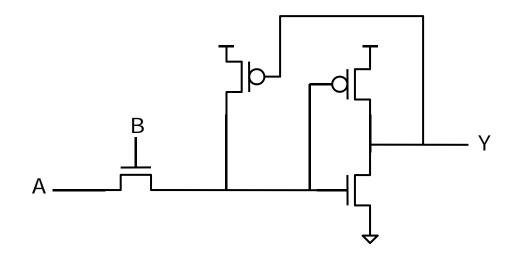

#### Pseudo-NMOS XOR Gate

An example of XOR gate realized with pseudo-NMOS logic

The XOR is defined by

$$Y = X_1 \oplus X_2 = X_1 \overline{X_2} + \overline{X_1} X_2 = \overline{X_1 \overline{X_2} + \overline{X_1} \overline{X_2}} = \overline{X_1 \overline{X_2} + \overline{X_1} \overline{X_2}} = \overline{X_1 \overline{X_2} + \overline{X_1} + \overline{X_2}}$$

# **Choosing Transistor Sizes**

#### 🗆 Goals

- Noise margin

- Power consumption

- Speed

- □ Noise margin

- It is affected by the low output voltage (V<sub>L</sub>)

- **V**<sub>L</sub> is determined by  $\beta_p / \beta_n$

- Speed

- The larger the W/L of the load transistor, the faster the gate will be, particularly when driving many other gates

- Unfortunately, this increases the power dissipation and the area of the driver network

# **Choosing Transistor Sizes**

Power dissipation

- A pseudo-NMOS logic gate having a "1" output has no static (DC) power dissipation.

- However, a pseudo-NMOS gate having a "O" output has a static power dissipation

- The static power dissipation is equal to the current of the PMOS load transistor multiplied by the power supply voltage. Thus, the power is given by

$$P_{dc} = \frac{\mu_{p} C_{ox}}{2} \left(\frac{W}{L}\right)_{P} \left(V_{gs} - V_{tp}\right)^{2} V_{dd}$$

- The large PMOS results in large power dissipation

- Power-reduction methods

- Select an appropriate PMOS

- Increase the bias voltage of PMOS

# **Choosing Transistor Sizes**

- A simple procedure for choosing transistor sizes of pseudo-NMOS logic gates

- The relative size (W/L) of the PMOS load transistor is chosen as a compromise between speed and size versus power dissipation

- Once the size of the load transistor has been chosen, then a simple procedure can be used to choose the W/Ls of the NMOS transistors in the NMOS network

- Let (W/L)<sub>eq</sub> be equal to one-half of the W/L of the PMOS load transistor

- For each transistor Q<sub>i</sub>, determine the maximum number of drive transistors it will be in series, for all possible inputs. Denote this number n<sub>i</sub>.

- □ Take  $(W/L)_i = n_i (W/L) eq$

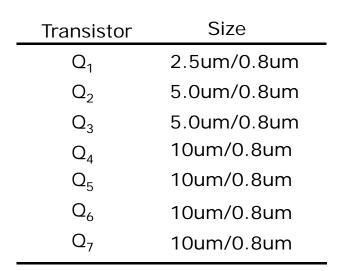

# An Example

- Choose appropriate sizes for the pseudo-NMOS logic gate shown below

- (W/L)<sub>8</sub> is 5 um/0.8 um

- (W/L)<sub>eq</sub> is (5/0.8)/2=3.125

- Gate lengths of drive transistors are taken at their minimum 0.8um

- Thus we can obtain

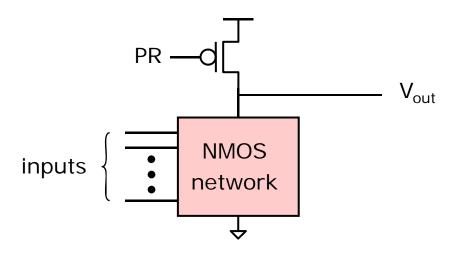

# Dynamic Logic

- To eliminate the static power dissipation of pseudo-NMOS logic

- An alternative technique is to use dynamic precharging called dynamic logic as shown below

Normally, during the time the output is being precharged, the NMOS network should not be conducting

This is usually not possible

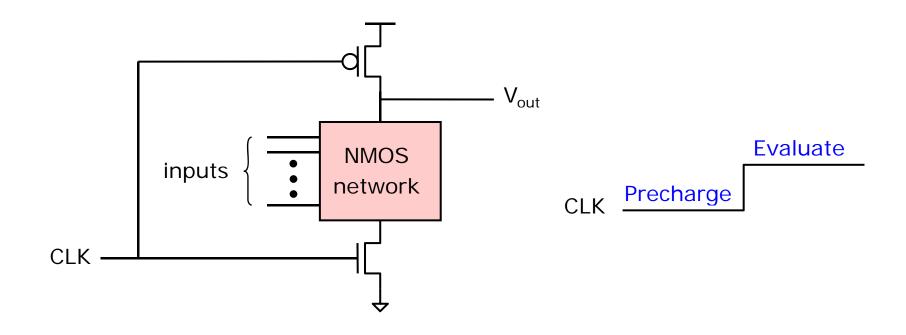

## Dynamic Logic

Another dynamic logic technique

Two-phase operation: precharge & evaluate

This can fully eliminate static power dissipation

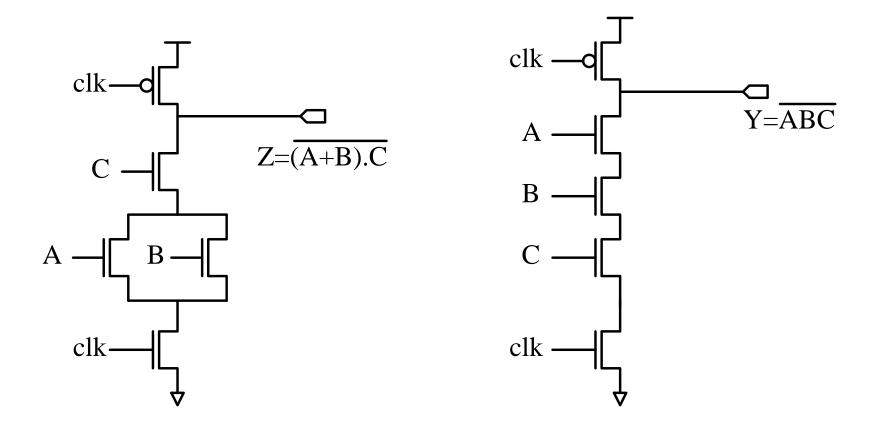

## Examples of Dynamic Logic

#### □ Two examples

# Problems of Dynamic Logic

- □ Two major problems of dynamic logic

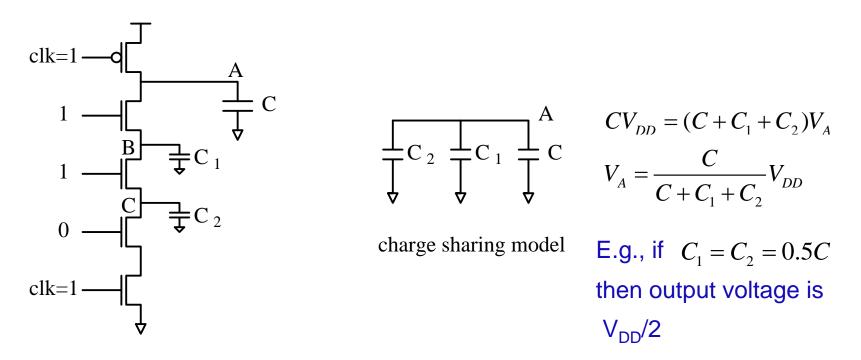

- Charge sharing

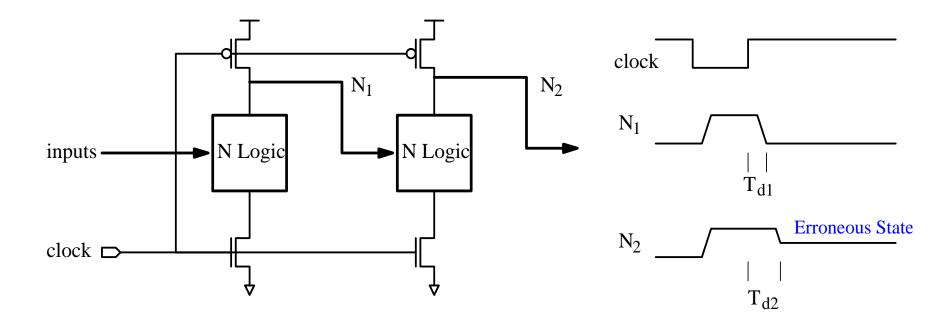

- Simple single-phase dynamic logic can not be cascaded

- Charge sharing

# Problems of Dynamic Logic

Simple single-phase dynamic logic can not be cascaded

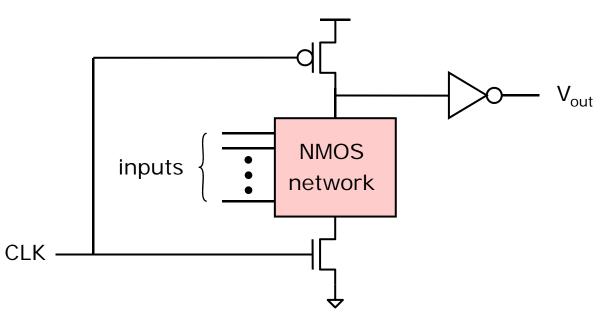

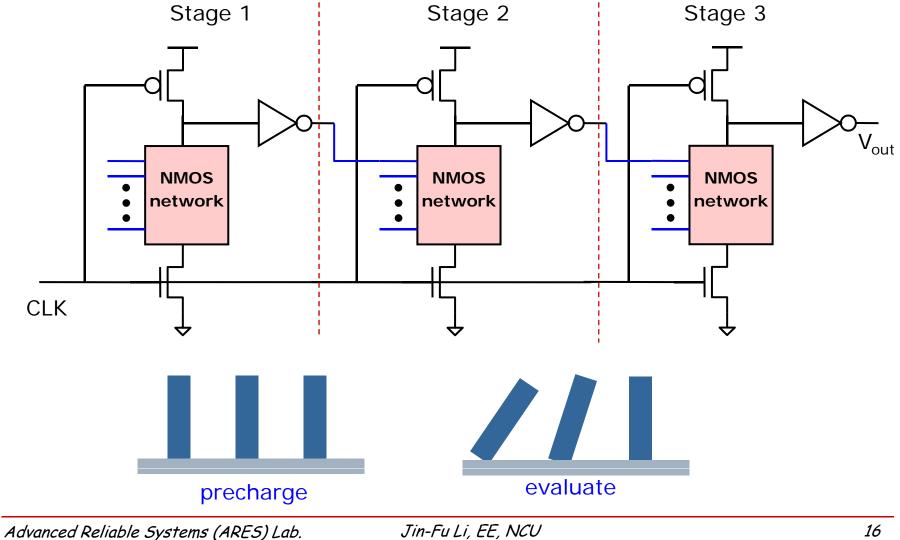

# CMOS Domino Logic

Domino logic can be cascaded

The basic structure of domino logic

- Some limitations of this structure

- Each gate must be buffered

- Only noninverting structures are possible

#### A Domino Cascade

#### □ An example of cascaded domino logics

# **Charge-Keeper Circuits**

- The domino cascade must have an evaluation interval that is long enough to allow every stage time to discharge

- This means that charge sharing and charge leakage processes that reduce the internal voltage may be limiting factors

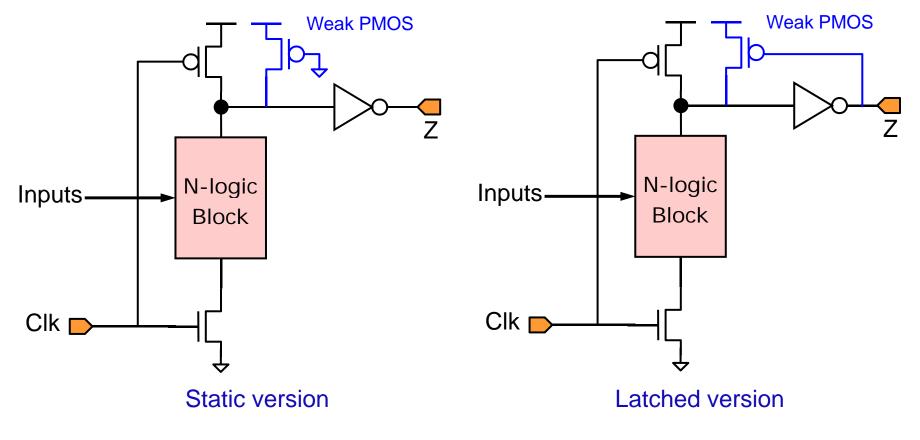

- Two types of modified domino logics can cope with this problem

- Static version

- Latched version

### **Charge-Keeper Circuits**

#### Modified domino logics

The aspect ratio of the charge-keeper MOS must be small so that it does not interfere with discharge event

Advanced Reliable Systems (ARES) Lab. Jin-Fu Li, EE, NCU

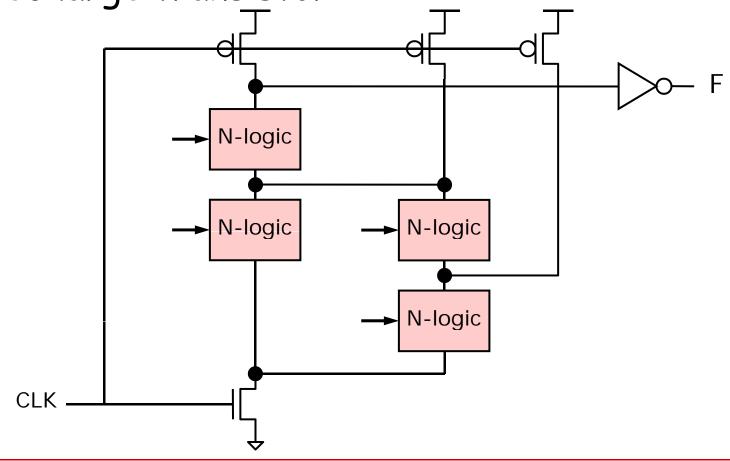

### **Complex Domino Gate**

In a complex domino gate, intermediate nodes have been provided with their own precharge transistor

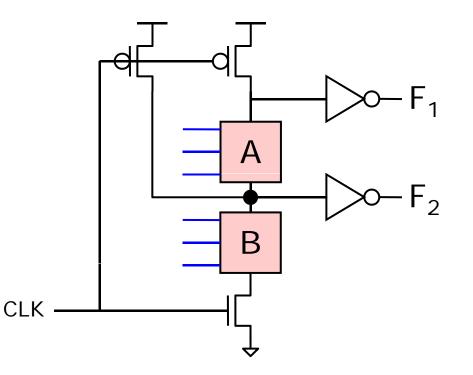

## Multiple-Output Domino Logic

- Multiple-output domino logic (MODL) allows two or more outputs from a single logic gate

- □ The basic structure of MODL

## A Multiple-Output Domino Logic Gate

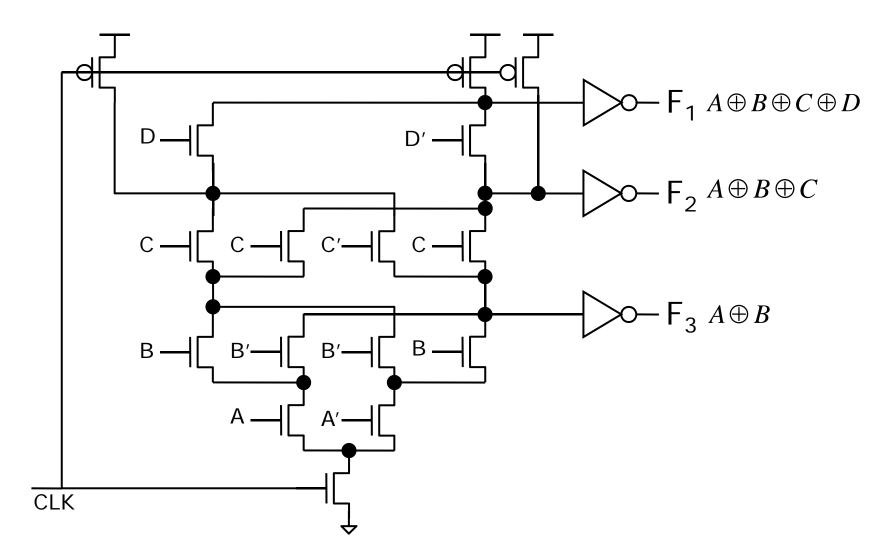

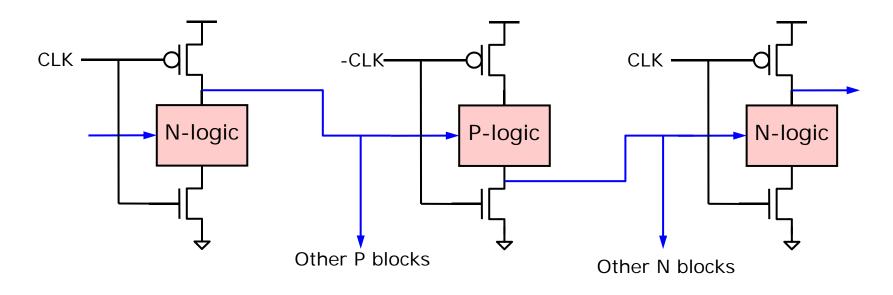

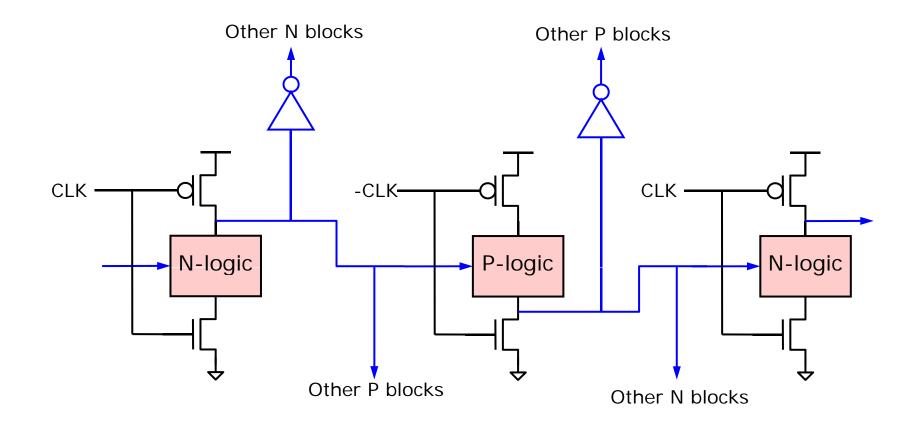

# NP Domino Logic

A further refinement of the domino logic is shown below

The domino buffer is removed, while cascaded logic blocks are alternately composed of P- and N-transistors

## NP Domino Logic

#### □ NP domino logic with multiple fanouts

#### Advanced CMOS Logic Design

#### Pass-Transistor Logic

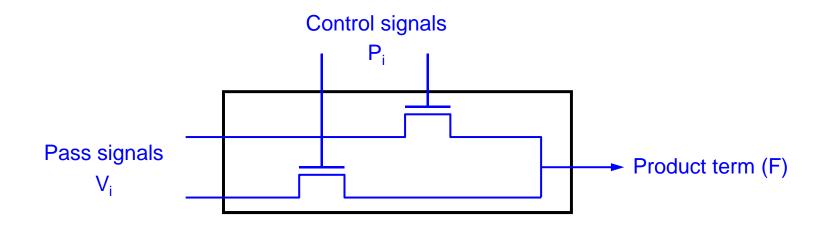

# Pass-Transistor Logic

□ Model for pass transistor logic

□ The product term

- F= $P_1V_1+P_2V_2+...+P_nV_n$

- The pass variables can take the values {0,1,X<sub>i</sub>,-X<sub>i</sub>,Z}, where X<sub>i</sub> and -X<sub>i</sub> are the true and complement of the *i*th input variable and Z is the high-impedance

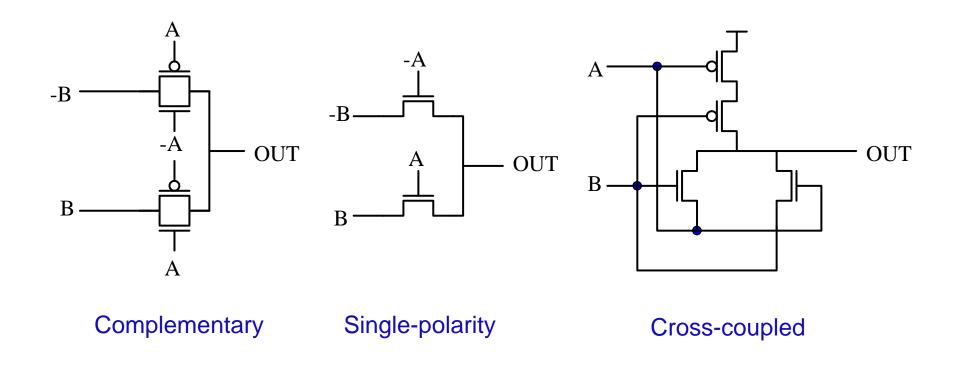

## **Pass-Transistor Logics**

Different types of pass-transistor logics for two-input XNOR gate implementation

# Full-Swing Pass-Transistor Logic

Modifying NMOS pass-transistor logic so full-level swings are realized

- Adding the additional PMOS has another advantages

- It adds hysteresis to the inverter, which makes it less likely to have glitches

# Differential Logic Design

#### Features of the differential logic design

- Logic inversions are trivially obtained by simply interchanging wires without incurring a time delay

- The load networks will often consist of two crosscoupled PMOS only. This minimizes both area and the number of series PMOS transistors

#### Disadvantage

Two wires must be used to represent every signal, the interconnect area can be significantly greater. In applications in which only a few close gates are being driven, this disadvantage is often not as significant as the advantages

# Thus differential logic circuits are often a preferable consideration

Advanced Reliable Systems (ARES) Lab. Jin-Fu Li, EE, NCU

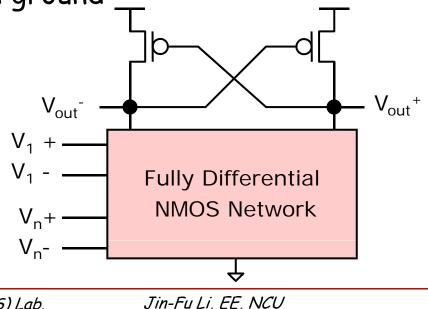

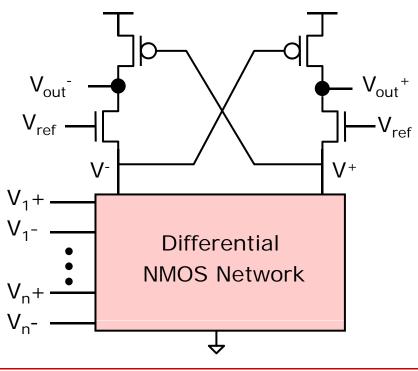

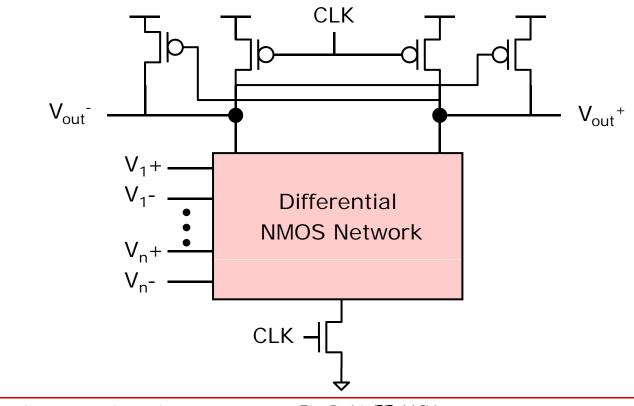

# A Fully Differential Logic Circuit

- One simple and popular approach for realizing differential logic circuit is shown below

- The inputs to the drive network come in pairs, a singleended signal and its inverse

- The NMOS network can be divided into two separate networks, one between the inverting output and ground, and a complementary network between the noninverting output and ground \_\_\_\_\_

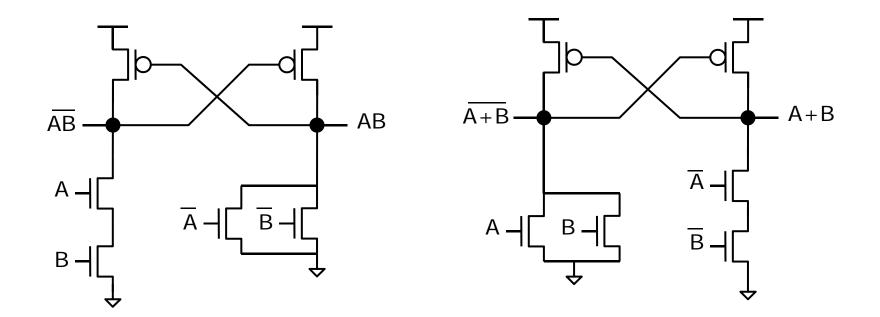

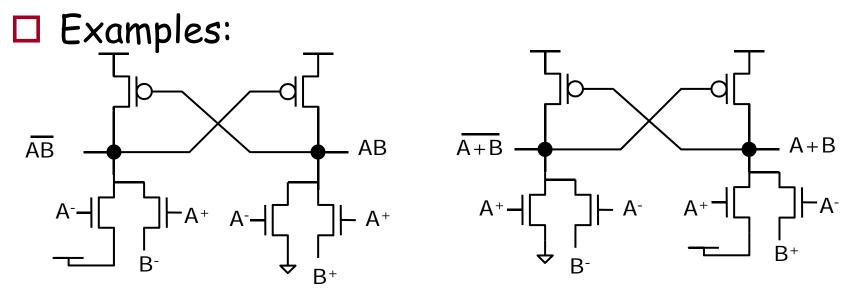

### Examples

Differential CMOS realizations of AND and OR functions

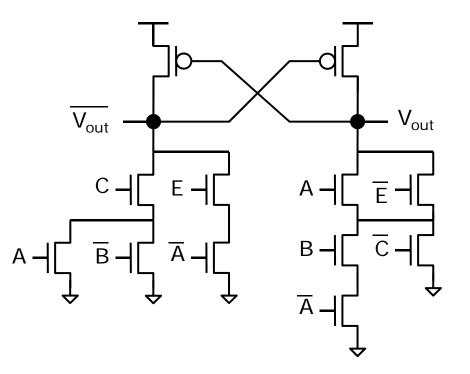

### Examples

# Differential CMOS realization of the function V<sub>out</sub>=(A+B')C+A'E

# Differential Split-Level Logic

- Differential split-level (DSL) logic

- A variation of fully differential logic

- A compromise between a cross-coupled load with no d.c. power dissipation and a continuously-on load with d.c. power dissipation

# **Differential Split-Level Logic**

- □ Features of DSL logic

- The loads have some of the features of both continuous loads and cross-coupled load

- Both outputs begin to change immediately

- The loads do have d.c. power dissipation, but normally much less than pseudo-NMOS gates and dynamic power dissipation

- The nodes V+, V-, and all internal nodes of the NMOS network have voltage changes between greater than OV and V<sub>ref</sub>-V<sub>tn</sub>

This reduced voltage swing increases the speed of the logic gates

The maximum drain-source voltage across the NMOS transistors is reduced by about one-half

1 This greatly minimizes the short-channel effects

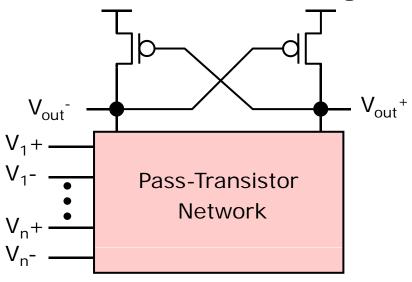

## **Differential Pass-Transistor Logic**

- It is not necessary to wait until one side goes to low before the other side goes high

- Pass-transistor networks for most required logic functions exist in which both sides of the crosscoupled loads are driven simultaneously

- This minimizes the time from when the inputs changes to when the low-to-high transition occurs

## **Differential Pass-Transistor Logic**

- □ Other features of pass-transistor logic

- It removes the ratio requirements on the logic and has guaranteed functionality

- The cross-coupled loads restore signal levels to full V<sub>dd</sub> levels, thereby eliminating the voltage drop

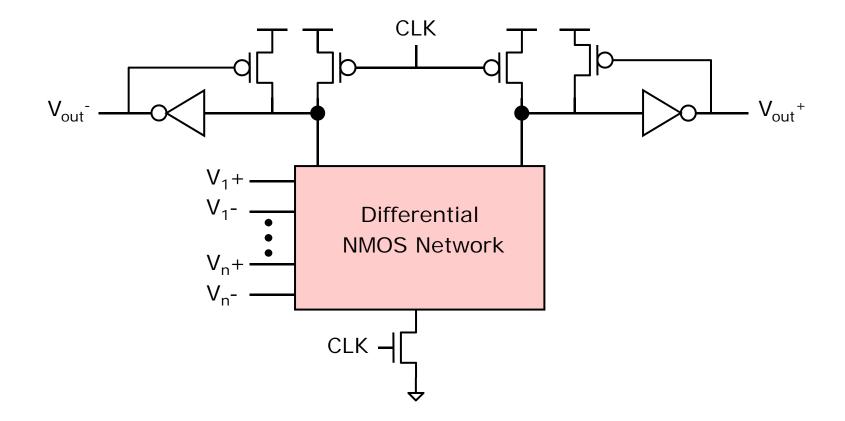

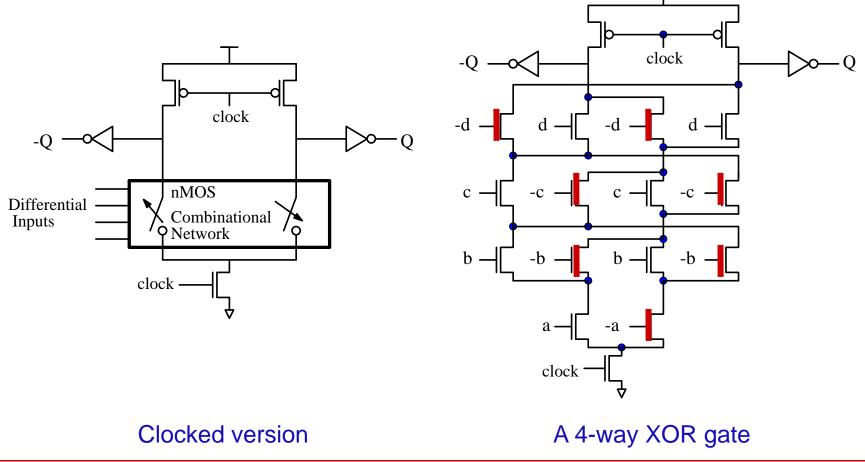

# Dynamic Differential Logic

□ A differential Domino logic gate

# Dynamic Differential Logic

- □ Features of dynamic Domino logic

- Its d.c. power dissipation is very small, whereas its its speed still quite good

- Because of the buffers at the output, its output drive capability is also very good

- One of major limitations of Domino logic, the difficulty in realizing inverting functions, is eliminated because of the differential nature of the circuits

# Dynamic Differential Logic

When the fan-out is small, the inverters at the output can be eliminated and the inputs to the charge-keeper transistors can be taken from the opposite output

# Dynamic Differential Logic

Dynamic differential logics without chargekeeper circuit (abcd)=(0000)

Advanced Reliable Systems (ARES) Lab.

Jin-Fu Li, EE, NCU

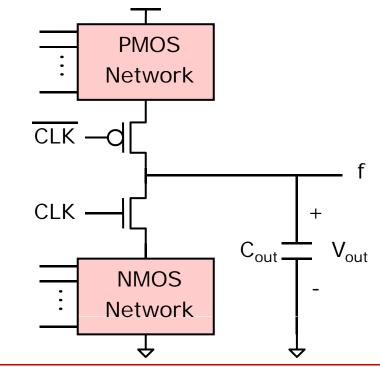

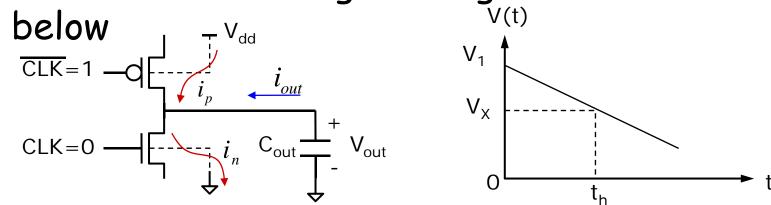

# Clocked CMOS (C<sup>2</sup>MOS)

- $\Box$  Structure of a C<sup>2</sup>MOS gate

- Ideally, clocks are non-overlapping  $\rightarrow_{CLK} X CLK=0$

- CLK=1, f is valid

- CLK=0, the output is in a high-impedance state. During this time interval, the output voltage is held on C<sub>out</sub>

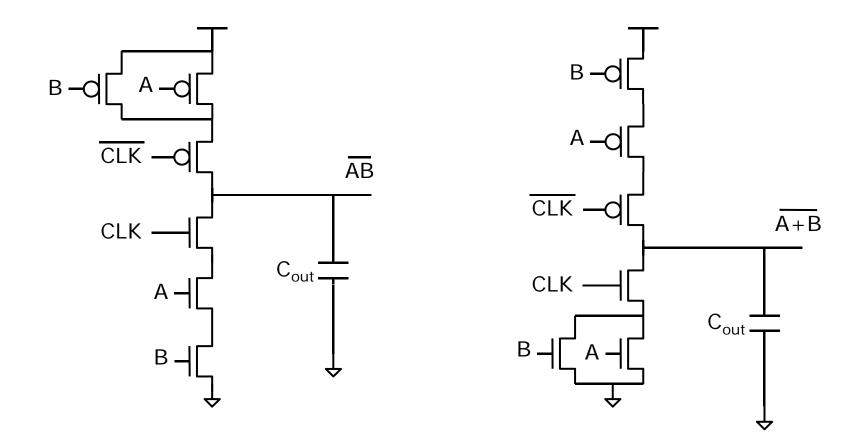

## Examples of C<sup>2</sup>MOS Logic Gates

### Gates

### □ The problem of charge leakage

- Cause that the output node cannot hold the charge on V<sub>out</sub> very long

- □ The basics of charge leakage are shown

Advanced Reliable Systems (ARES) Lab.

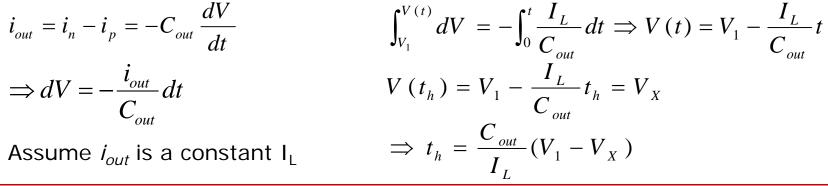

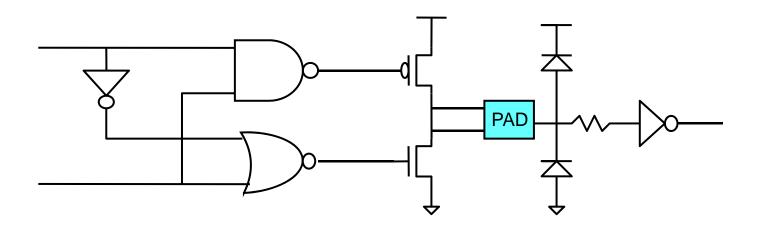

# I/O Pads

### Types of pads

- V<sub>dd</sub>, V<sub>ss</sub> pad

- Input pad (ESD)

- Output pad (driver)

- I/O pad (ESD+driver)

- All pads need guard ring for latch-up protection

# Core-limited pad & pad-limited pad

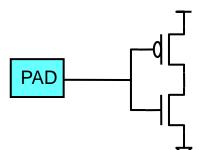

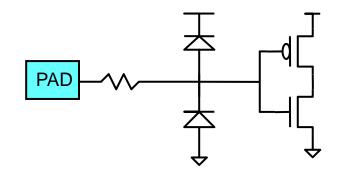

## **ESD** Protection

Input pad without *electrostatic discharge* (ESD) protection

Assume I=10uA, C<sub>g</sub>=0.03pF, and t=1us

The voltage that appears on the gate is about 330volts

Input pad with ESD protection

### **Tristate & Bidirectional Pads**

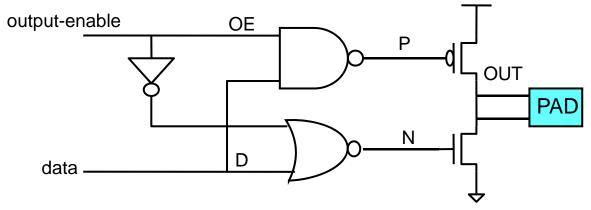

#### □ Tristate pad

| OE | D | Ν | Ρ | OUT |

|----|---|---|---|-----|

| 0  | Х | 0 | 1 | Z   |

| 1  | 0 | 1 | 1 | 0   |

| 1  | 1 | 0 | 0 | 1   |

Bidirectional pad

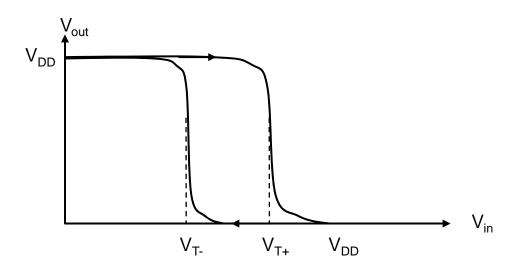

# Schmitt Trigger Circuit

Voltage transfer curve of Schmitt circuit

Hysteresis voltage V<sub>H</sub>=V<sub>T+</sub>-V<sub>T-</sub>

When the input is rising, it switches when V<sub>in</sub>=V<sub>T+</sub>

When the input is falling, it switches when V<sub>in</sub>=V<sub>T-</sub>

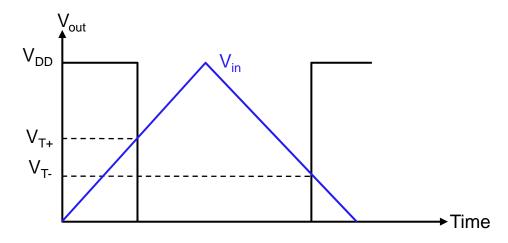

# Schmitt Trigger Circuit

Voltage waveform for slow input

Schmitt trigger turns a signal with a very slow transition into a signal with a sharp transition

# Schmitt Trigger Circuit

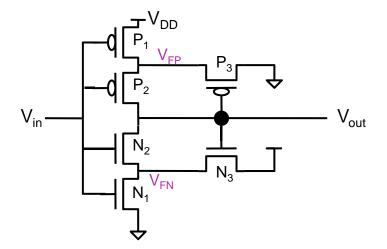

A CMOS version of the Schmitt trigger circuit

- When the input is rising, the  $V_{GS}$  of the transistor  $N_2$  is given by  $V_{GS} = V_{in} - V_{FN}$

- When  $V_{in} = V_{T+}$ ,  $N_2$  enters in conduction mode which means  $V_{GS2} = V_{Tn}$

$$\blacksquare \quad \text{Then} \quad V_{FN} = V_{T+} - V_{Tn}$$

# Summary

- The following topics have been introduced in this chapter

- CMOS Logic Gate Design

- Advanced CMOS Logic Design

- Clocking Strategies

- I/O Structures