# **Chapter 1 Introduction to Memories**

Jin-Fu Li Advanced Reliable Systems (ARES) Lab. Dept. of Electrical Engineering National Central University Jhongli, Taiwan

# Outline

- Importance of Embedded Memories

- Overview of Memory Structures

# Embedded Memory – The Key to SOC

- Embedded memory is becoming more central to integrated circuit design

- Historically, ICs were dominated by the logic functions, with memory being external

- Today, an SOC contains many memory blocks of different sizes, shapes and functionality

- Typically, embedded memories represent about 30%~50% SOC area

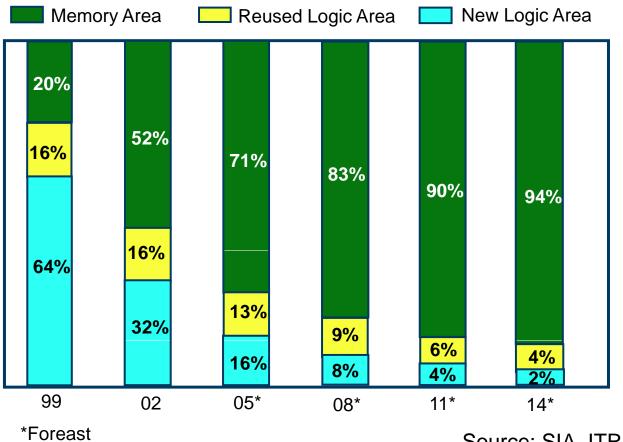

- The Semiconductor Industry Association (SIA) predicts that 90% of the SOC's surface will be memory in 2011

## Embedded Memory – The Key to SOC

• SOC memory continues to increase

Source: SIA, ITRS, 2000

National Central University

# **Embedded Memory –** Advantages

- Area

- Embedding multiple memories on a single SOC reduces the amount of silicon used

- Performance

- Embedding faster, wider memories and moving them closer to processor can increase system performance substantially

- Power

- Embedded memories eliminate the need to drive off-chip capacitance between the stand-alone memories and other system chips

- Design reuse

- By reusing embedded memories, system designers can significantly reduce develop time and cost

# **Embedded Memory –** Quality

- During manufacture

- Yield

- Exponential yield model

- $Y = e^{-\sqrt{AD}}$ , where *A* and *D* denote the area and defect density, respectively

- After manufacture – Reliability

- During use

- Soft error rate

# **Quality During Manufacture**

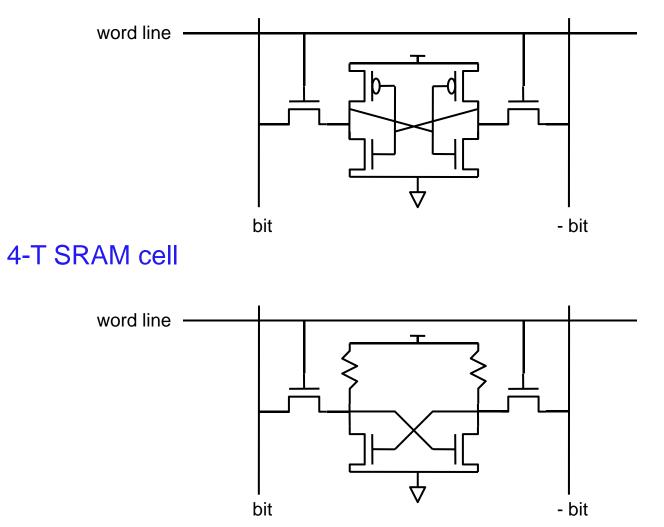

- Issues of embedded memory

- As the density of transistors is increased, the D is increased compared to logic

- About 2X logic for high density 6-T SRAM

- Solutions

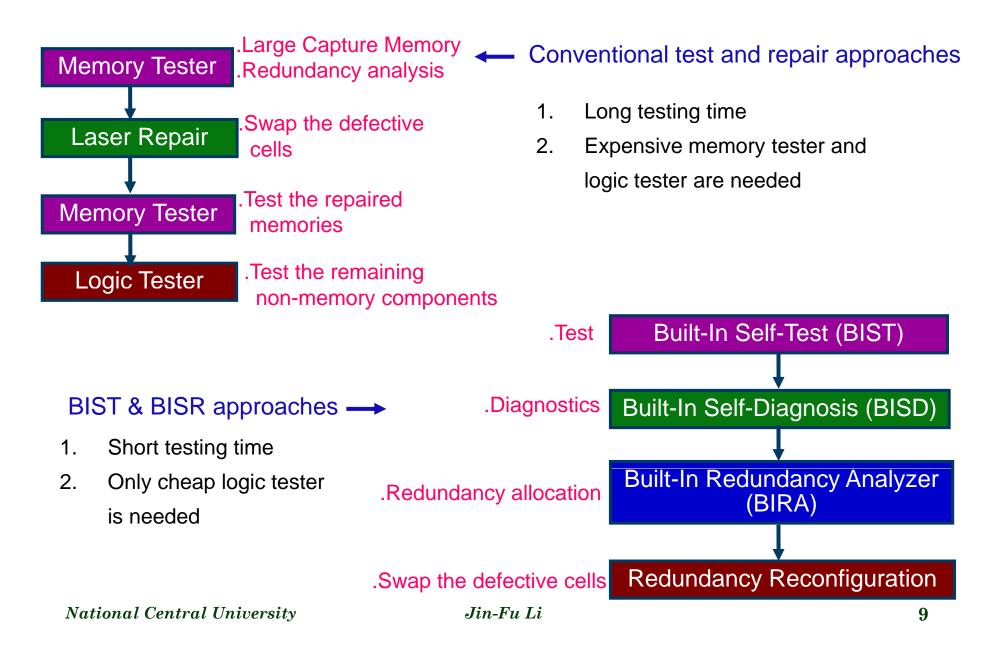

- Redundancy & laser repair using ATE

- Error correction code (ECC)

- Redundancy & repair

- Achieve yield parity with logic, or better

- About 3% area overhead

- Recommended over 1Mb

# **Quality During Manufacture**

- Corrects <5 defects per Mb</li>

- Laser repair manufacturing flow

- ECC

- Detect/repair defects in individual words

- 25-30% area overhead

- \* Ex: 6 extra bits for single bit correction in 32 bit words

- Latency penalty

- \* At least one clock cycle latency penalty

#### **Quality-Insurance Strategies for Memories**

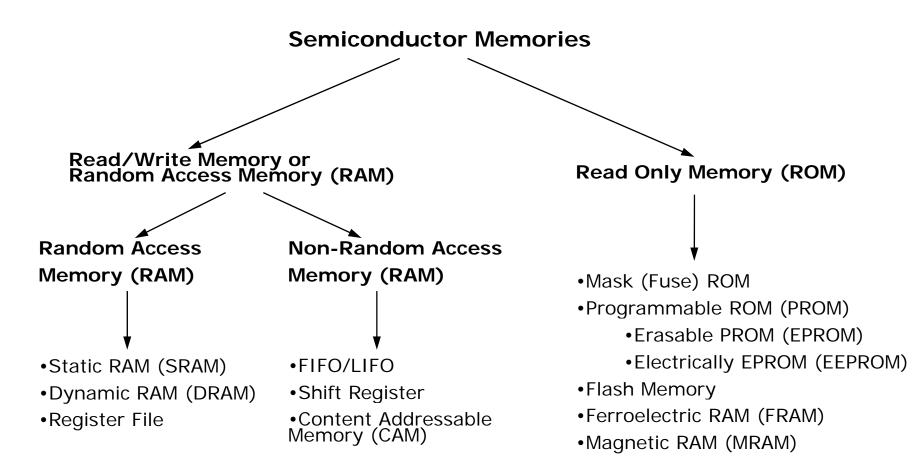

# **Introduction to Memories**

• Overview of semiconductor memory types

## Memory Elements – Memory Architecture

- Volatile memories may be divided into the following categories

- Random access memory

- Serial access memory

- Content addressable memory

- Memory architecture

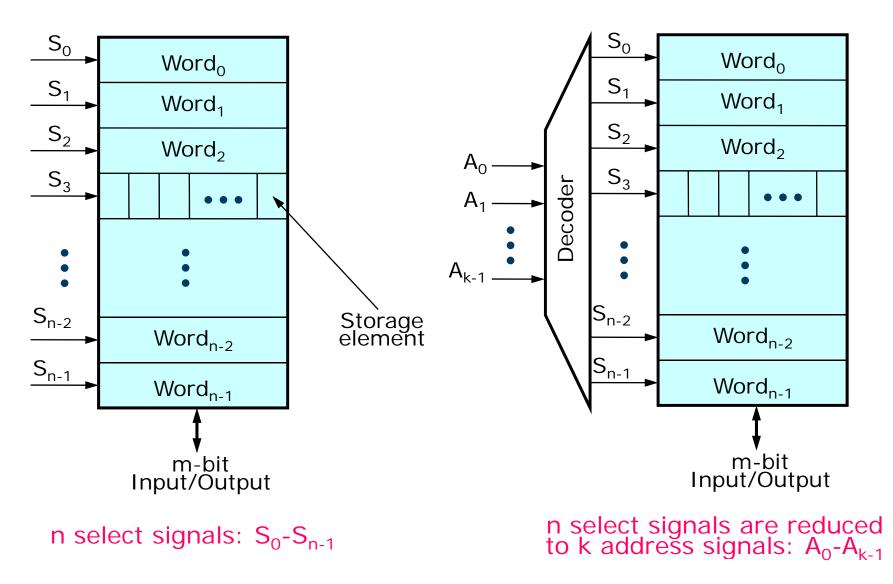

## **1-D Memory Architecture**

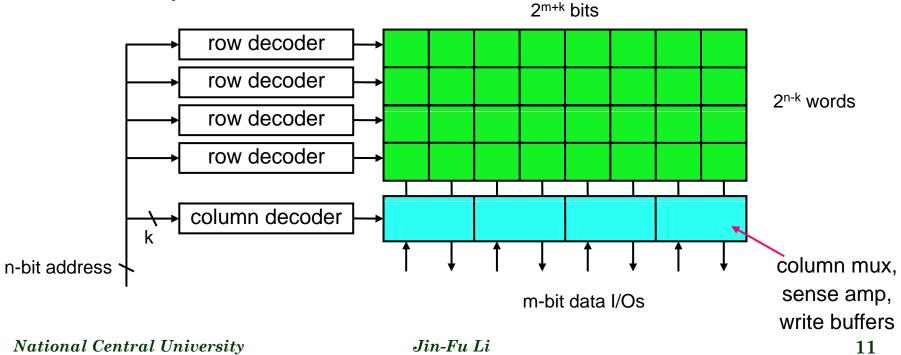

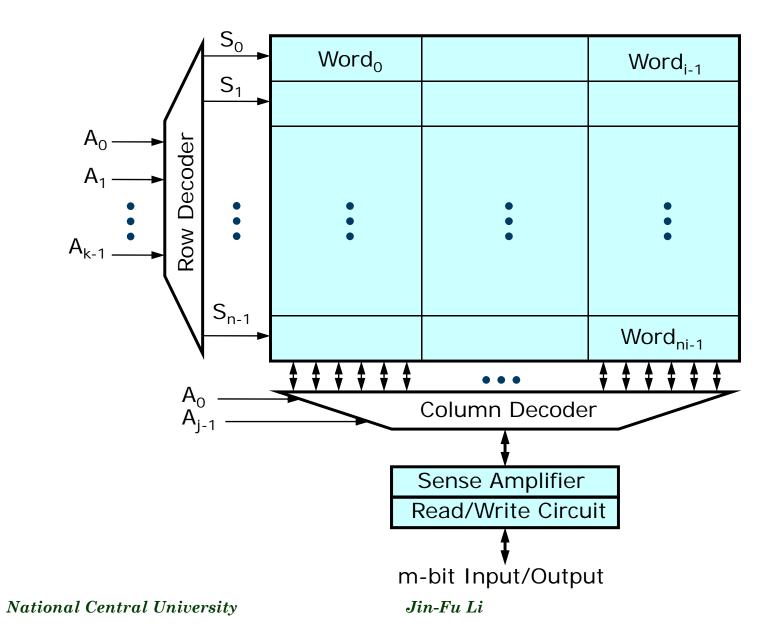

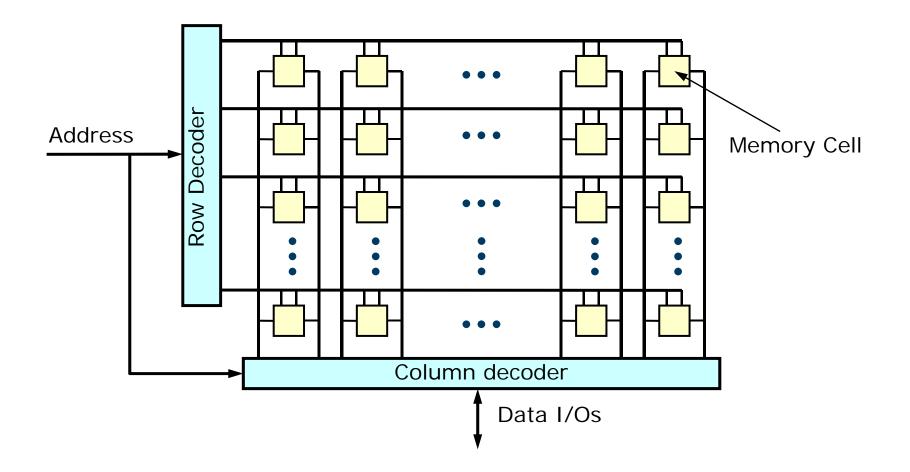

## **2-D Memory Architecture**

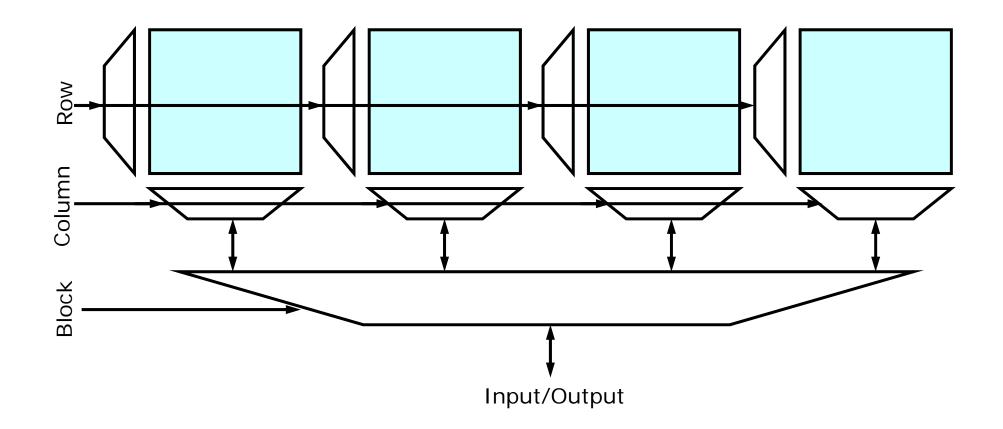

### **3-D Memory Architecture**

### **Conceptual 2-D Memory Organization**

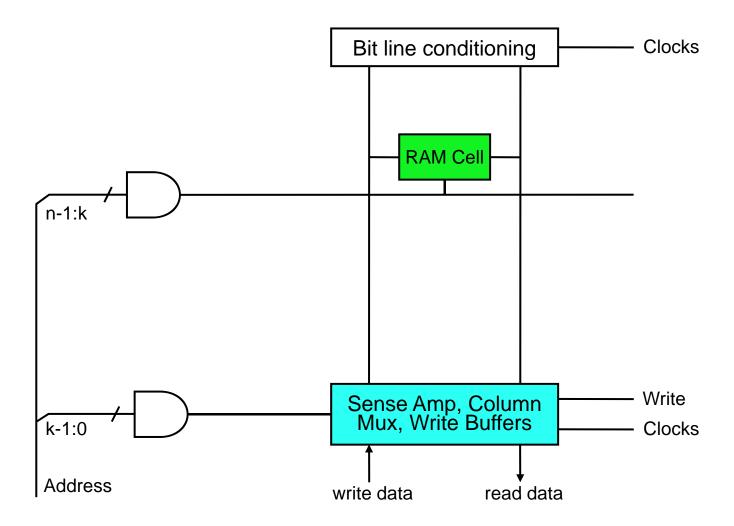

## **Memory Elements – RAM**

#### Generic RAM circuit

National Central University

### Memory Elements – RAM Cells

6-T SRAM cell

National Central University

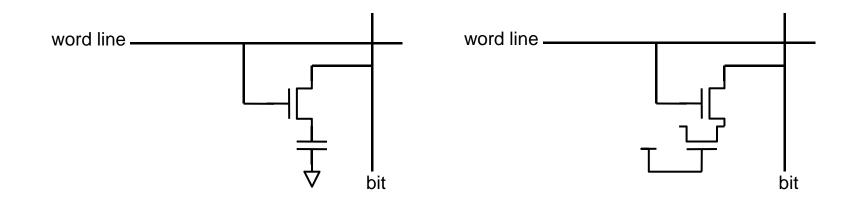

## Memory Elements – RAM Cells

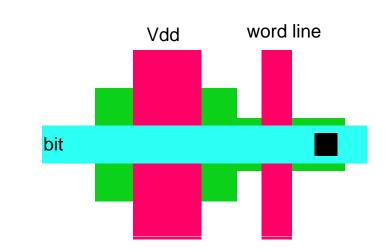

1-T DRAM cell

Layout of 1-T DRAM (right)

National Central University

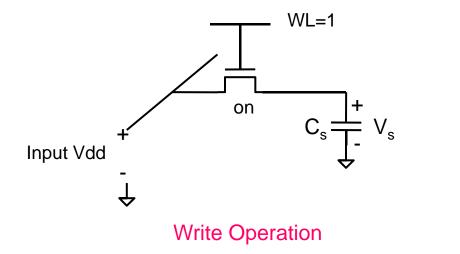

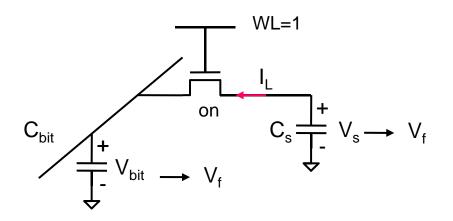

#### Memory Elements – DRAM Retention Time

Write and hold operations in a DRAM cell

$$V_{s} = V_{\text{max}} = V_{DD} - V_{tn}$$

$$Q_{\text{max}} = C_{s} (V_{DD} - V_{tn})$$

National Central University

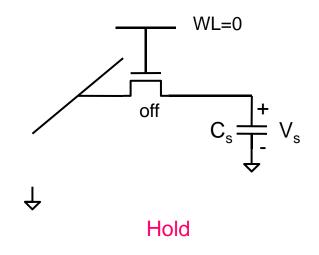

#### Memory Elements – DRAM Retention Time

Charge leakage in a DRAM Cell

$$I_{L} = -\left(\frac{dQ_{s}}{dt}\right)$$

$$I_{L} = -C_{s}\left(\frac{dV_{s}}{dt}\right)$$

$$I_{L} \approx -C_{s}\left(\frac{\Delta V_{s}}{\Delta t}\right)$$

$$t_{h} = |\Delta t| \approx \left(\frac{C_{s}}{I_{L}}\right) \Delta V_{s}$$

National Central University

Jin-Fu Li

20

#### Memory Elements – DRAM Refresh Operation

As an example, if IL=1nA, Cs=50fF, and the difference of Vs is 1V, the hold time is

$$t_h = \frac{50 \times 10^{-15}}{1 \times 10^{-9}} \times 1 = 0.5 \,\mu s$$

Memory units must be able to hold data so long as the power is applied. To overcome the charge leakage problem, DRAM arrays employ a **refresh operation** where the data is periodically read from every cell, amplified, and rewritten.

The refresh cycle must be performed on every cell in the array with a minimum refresh frequency of about

$$f_{refresh} \approx \frac{1}{2t_h}$$

National Central University

#### Memory Elements – DRAM Read Operation

$$Q_{s} = C_{s}V_{s}$$

$$Q_{s} = C_{s}V_{f} + C_{bit}V_{f}$$

$$V_{f} = \left(\frac{C_{s}}{C_{s} + C_{bit}}\right)V_{s}$$

This shows that  $V_f < V_s$  for a store logic 1. In practice,  $V_f$  is usually reduced to a few tenths of a volt, so that the design of the sense amplifier becomes a critical factor

National Central University

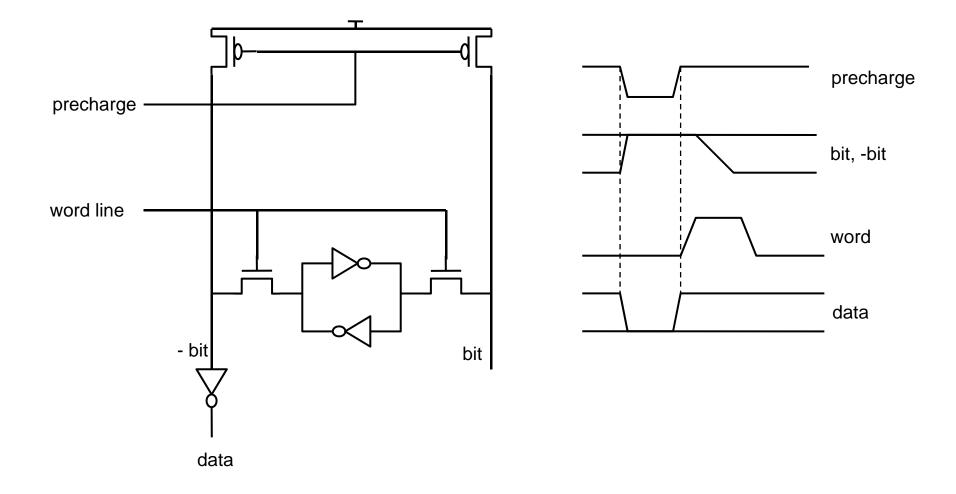

## Memory Elements – RAM Read Operation

National Central University

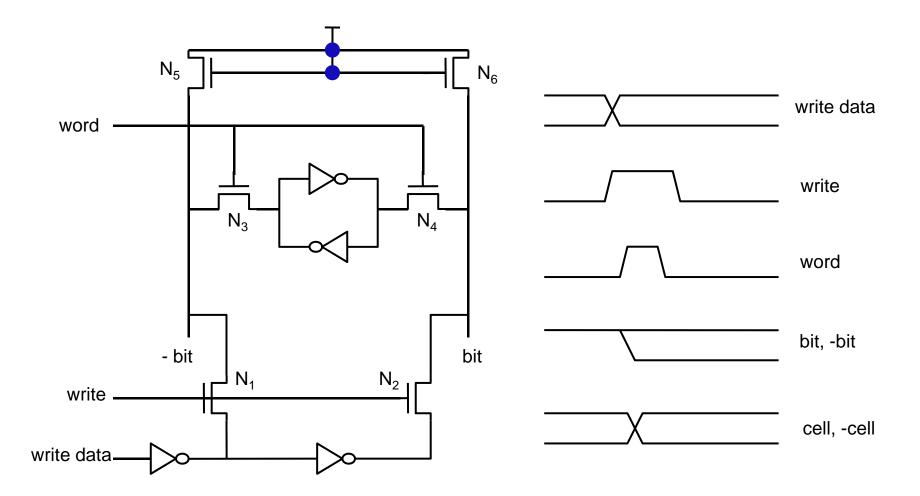

### Memory Elements – RAM Write Operation

National Central University

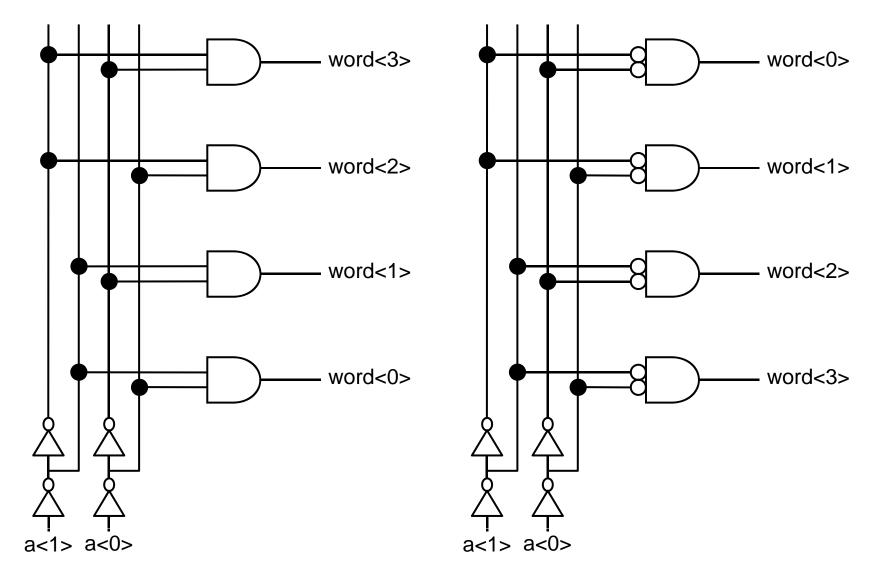

#### Memory Elements – Row Decoder

National Central University

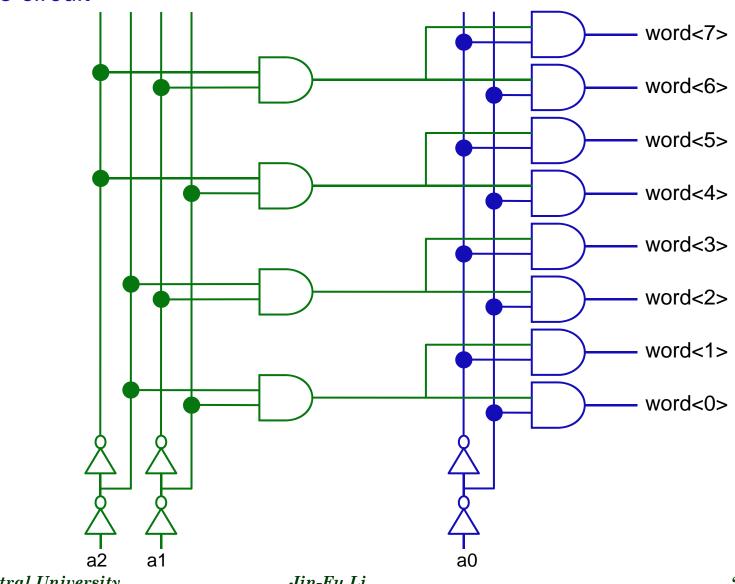

### Memory Elements – Row Decoder

Predecode circuit

National Central University

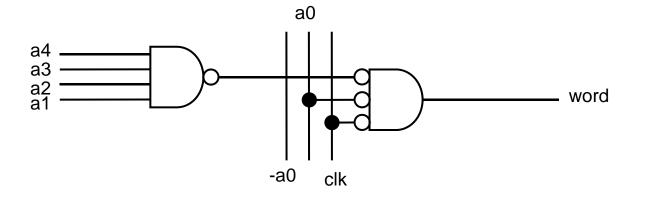

### Memory Elements – Row Decoder

Actual implementation

Pseudo-nMOS example  $a0 \longrightarrow contract of a co$

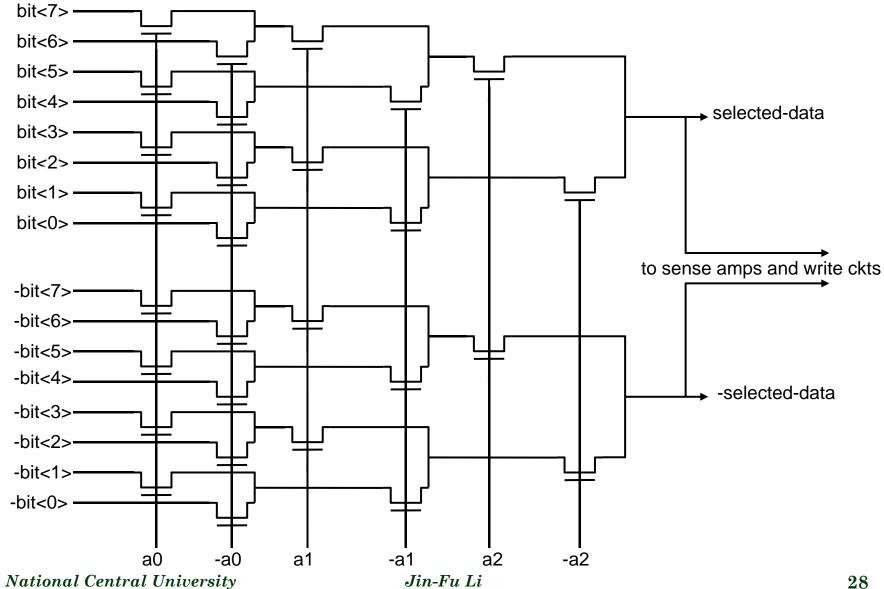

#### Memory Elements – Column Decoder

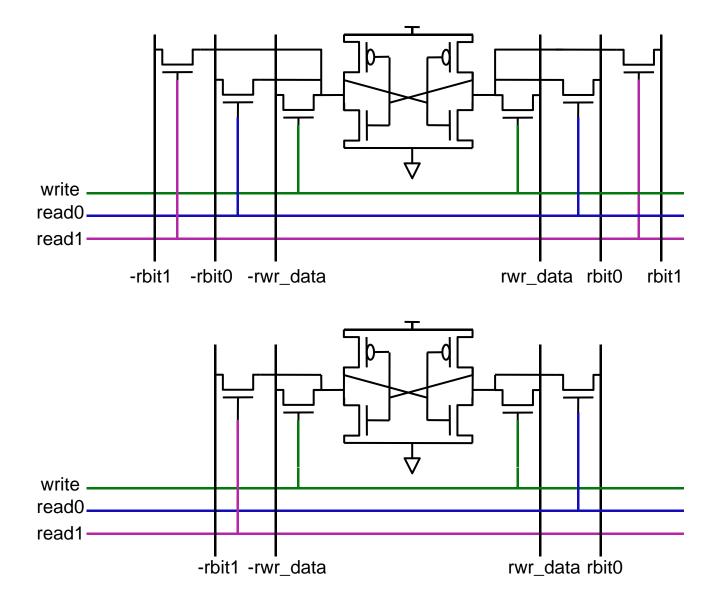

#### Memory Elements – Multi-Ported RAM

National Central University

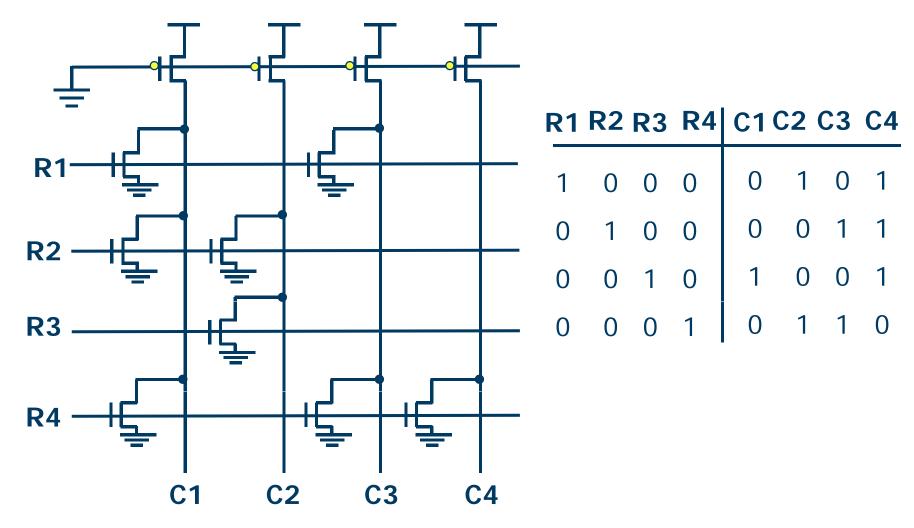

## **Memory Elements – ROM**

A 4x 4-bit NOR-based ROM array

National Central University

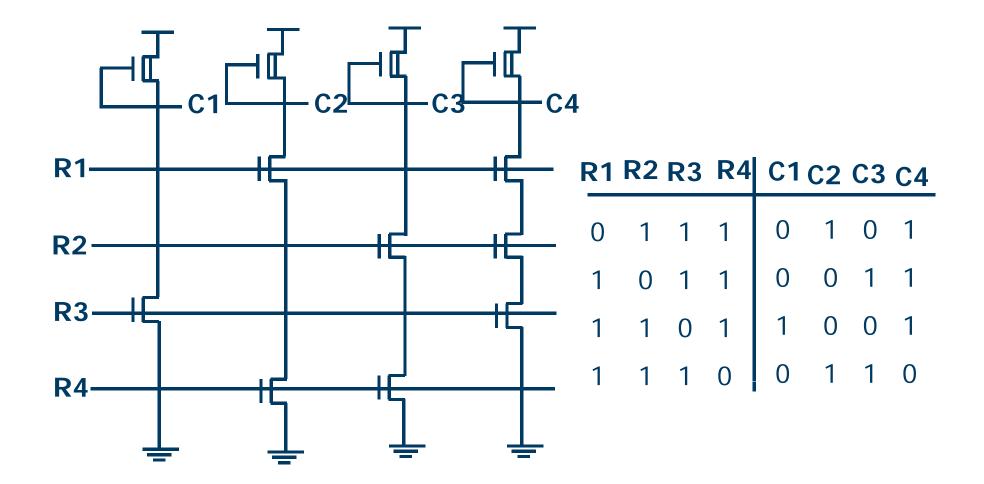

## **Memory Elements –** ROM

A 4x 4-bit NAND-based ROM array

## **Memory Elements –** ROM

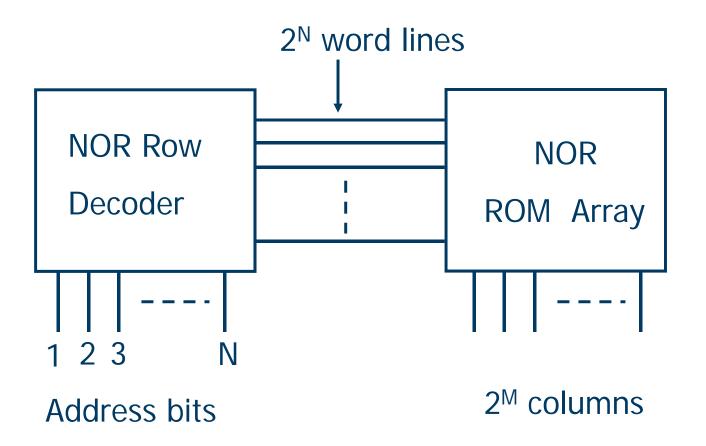

Typical ROM architecture