# **Chapter 5 VLSI Testing**

#### Jin-Fu Li

Advanced Reliable Systems (ARES) Laboratory Department of Electrical Engineering National Central University Jungli, Taiwan

#### Outline

- Basics

- □ Fault Modeling

- Design-for-Testability

#### Outline

#### Basics

- □ Fault Modeling

- Design-for-Testability

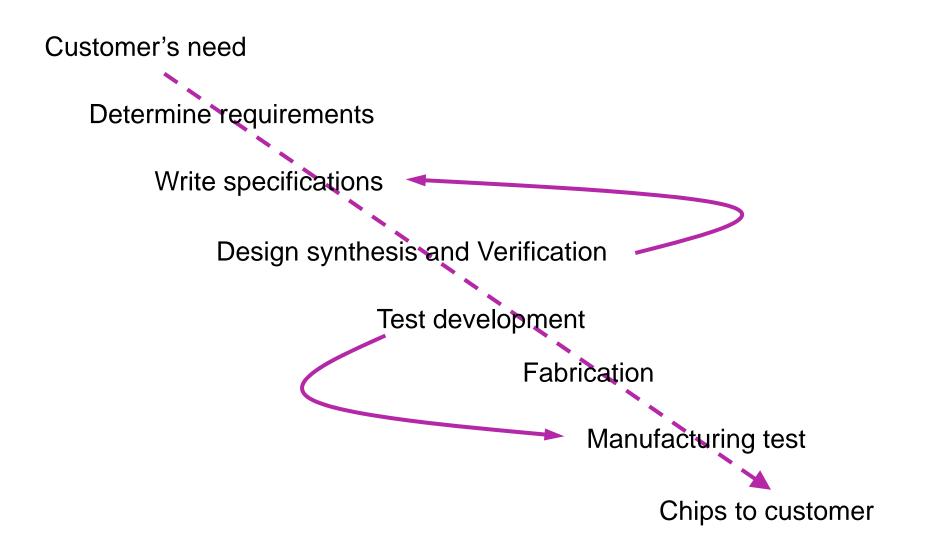

#### **VLSI Realization Process**

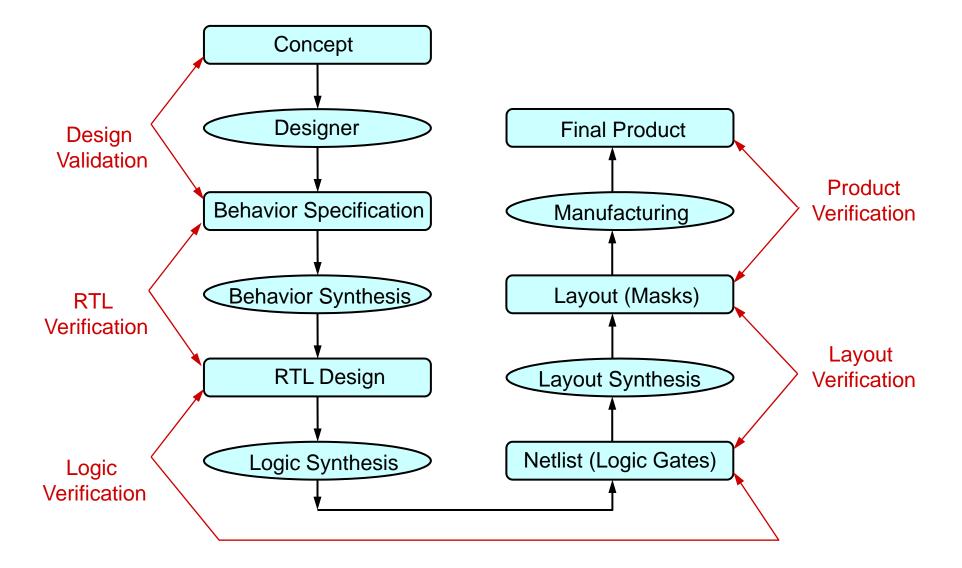

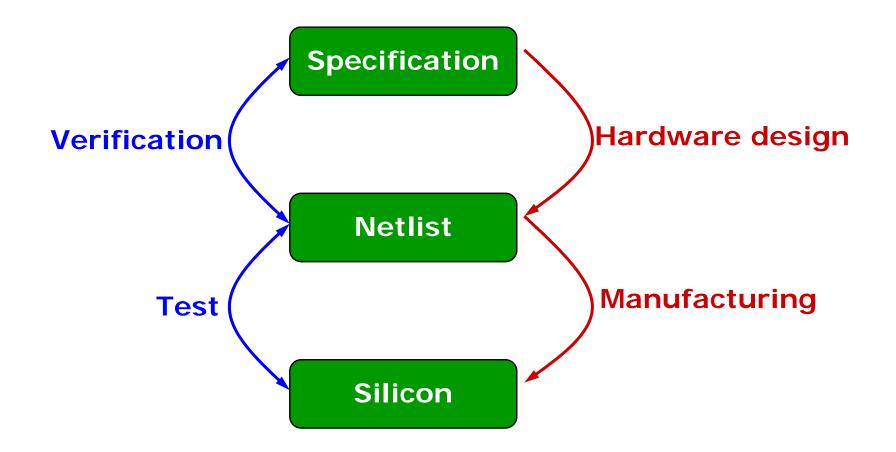

### **VLSI Design Cycle**

### **Role of Testing**

- If you design a product, fabricate, and test it, and it fails the test, then there must be a cause for the failure

- Test was wrong

- The fabrication process was faulty

- The design was incorrect

- The specification problem

- The role of *testing* is to detect whether something went wrong and the role of *diagnosis* is to determine exactly what went wrong

- Correctness and effectiveness of testing is most important for quality products

### **Benefits of Testing**

- Quality and economy are two major benefits of testing

- The two attributes are greatly dependent and can not be defined without the other

- Quality means satisfying the user's needs at a minimum cost

- The purpose of testing is to weed out all bad products before they reach the user

- The number of bad products heavily affect the price of good products

- A profound understanding of the principles of manufacturing and test is essential for an engineer to design a quality product

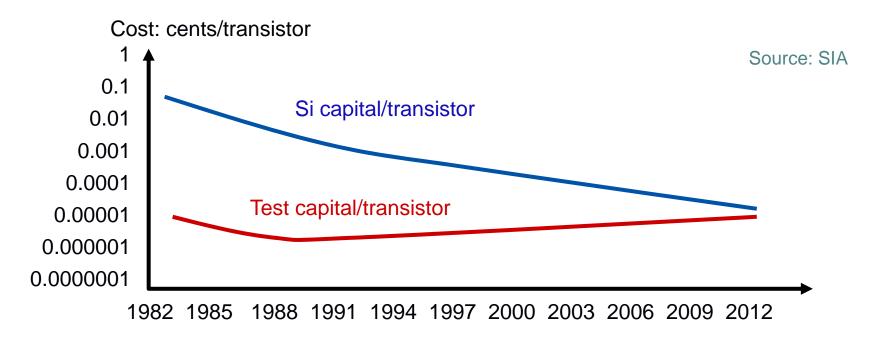

### **Trends of Testing**

- Two key factors are changing the way of VLSI ICs testing

- The manufacturing test cost has been not scaling

- The effort to generate tests has been growing geometrically along with product complexity

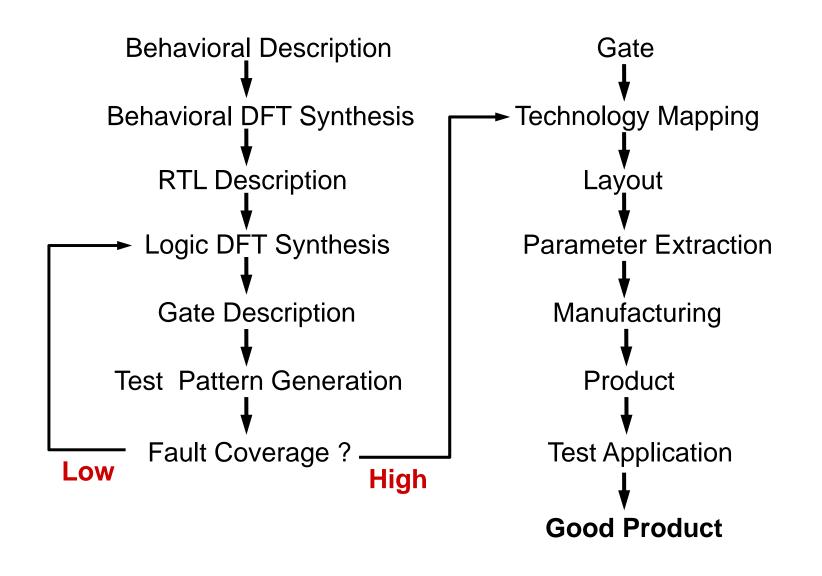

### **DFT Cycle**

### As Technology Scales Continuously

- Die size, chip yield, and design productivity have so far limited transistor integration in a VLSI design

- Now the focus has shifted to energy consumption, power dissipation, and power delivery

- As technology scales further we will face new challenges, such as variability, single-event upsets (soft errors), and device (transistor performance) degradation— these effects manifesting as inherent *unreliability* of the components, posing design and test challenges

Source: S. Borkar (Intel Corp.), IEEE Micro, 2005

Jin-Fu Li, EE, NCU

#### Possible Solution to Conquer Unreliability

The key to the reliability problem might be to exploit the abundance of transistors—use Moore's low to advantage. Instead of relying on higher and higher frequency of operation to deliver higher performance, a shift toward parallelism to deliver higher performance is in order, and thus multi might be the solution at all levels—from multiplicity of functional blocks to multiple processor cores in a system

Source: S. Borkar (Intel Corp.), IEEE Micro, 2005

#### Possible Solution to Conquer Unreliability

We could distribute test functionality as a part of the hardware to dynamically detect errors, or to correct and isolate aging and faulty hardware. Or a subset of cores in the multicore design could perform this work. This microarchitecture strategy, with multicores to assist in redundancy, is called **resilient microarchitecture**. It continuously detects errors, isolates faults, confines faults, reconfigures the hardware, and thus adapts. If we can make such a strategy work, there is no need for ontime factory testing, burn in, since the system is capable of testing and reconfiguring itself to make itself work reliably throughout its lifetime.

Source: S. Borkar (Intel Corp.), IEEE Micro, 2005

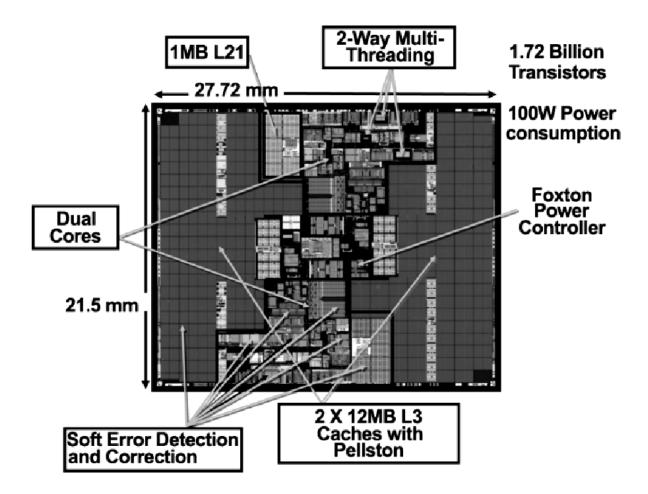

#### Itanium (JSSC, Jan. 2006)

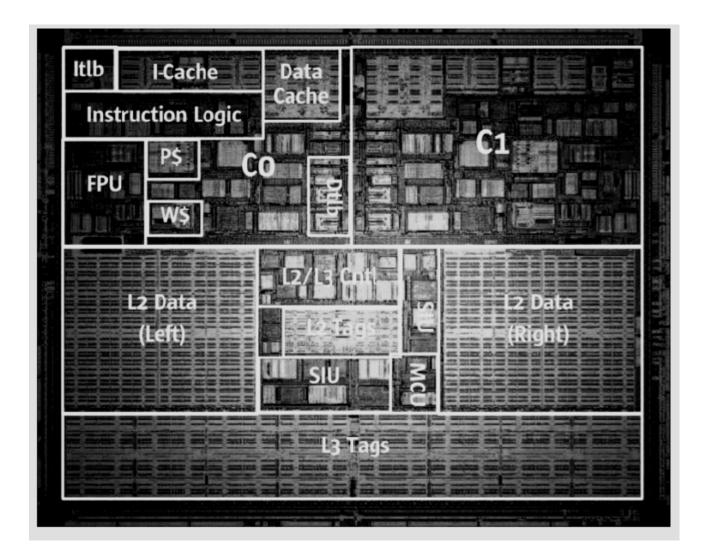

#### SPARC V9 (JSSC, Jan. 2006)

Advanced Reliable Systems (ARES) Lab.

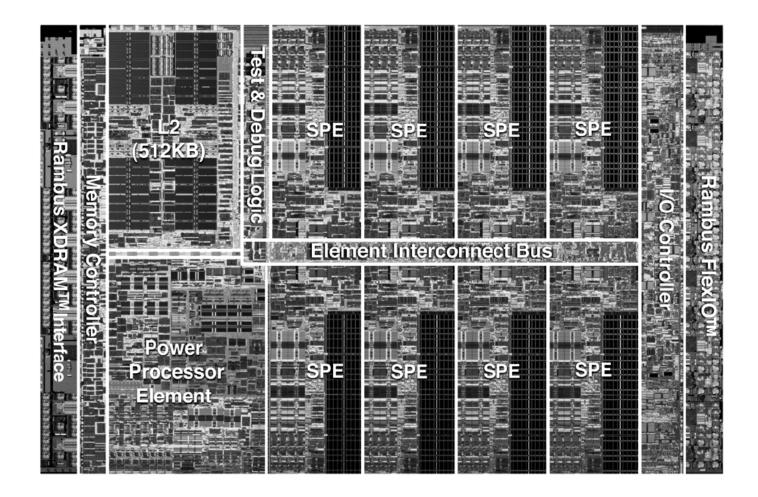

#### Cell Processor (JSSC, Jan. 2006)

#### **Verification & Test**

- Verifies correctness of design

- Performed by simulation, hardware emulation, or

#### Verification

- Perform once before manufacturing

- Responsible for quality of design

- Verifies correctness of manufactured hardware

- Two-part process

formal methods

- Test generation: software process executed once during design

- Fest application: electrical tests applied to hardware

- Test application performed on every manufactured device

- Responsible for quality of device

Test

#### **Verification & Test**

Reconvergent path model

### Defect, Fault, and Error

#### Defect

- A defect is the unintended difference between the implemented hardware and its intended design

- Defects occur either during manufacture or during the use of devices

- Fault

- A representation of a *defect* at the abstracted function level

- Error

- A wrong output signal produced by a defective system

- An error is caused by a *Fault* or a design error

### **Typical Types of Defects**

#### Extra and missing material

- Primarily caused by dust particles on the mask or wafer surface, or in the processing chemicals

- Oxide breakdown

- Primarily caused by insufficient oxygen at the interface of silicon (Si) and silicon dioxide (SiO<sub>2</sub>), chemical contamination, and crystal defects

- Electromigration

- Primarily caused by the transport of metal atoms when a current flows through the wire

- Because of a low melting point, aluminum has large self-diffusion properties, which increase its electromigration liability

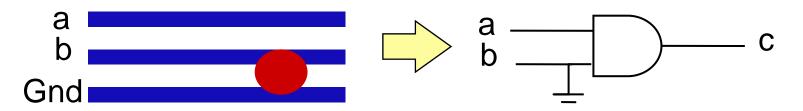

Example

□ Consider one two-input AND gate

Defect: a short to ground

- □ Fault: signal b stuck at logic 0

- Error: a=1, b=1, c=0 (correct output c=1)

- Note that the error is not permanent. As long as at least one input is 0, there is no error in the output

Advanced Reliable Systems (ARES) Lab.

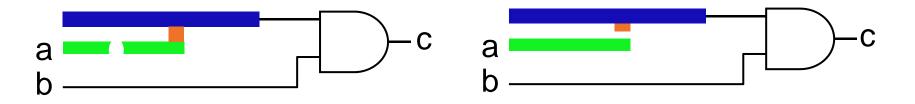

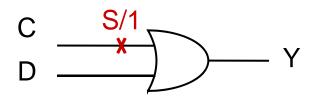

### Defect, Fault, and Error

Different types of defects may cause the same fault

- Different types of faults may cause the same error

- E.g., A stuck-at-0, Y=1; C stuck-at-1, Y=1

| С | D | Y | Y(C is S/1) |

|---|---|---|-------------|

| 0 | 0 | 0 | 1           |

| 0 | 1 | 1 | 1           |

| 1 | 0 | 1 | 1           |

| 1 | 1 | 1 | 1           |

#### Ideal Tests & Real Tests

#### The problems of ideal tests

- Ideal tests detect all defects produced in the manufacturing process

- Ideal tests pass all functionally good devices

- Very large numbers and varieties of possible defects need to be tested

- Difficult to generate tests for some real defects

- Real tests

- Based on analyzable fault models, which may not map on real defects

- Incomplete coverage of modeled faults due to high complexity

- Some good chips are rejected. The fraction (or percentage) of such chips is called the *yield loss*

- Some bad chips pass tests. The fraction (or percentage) of bad chips among all passing chips is called the *defect level*

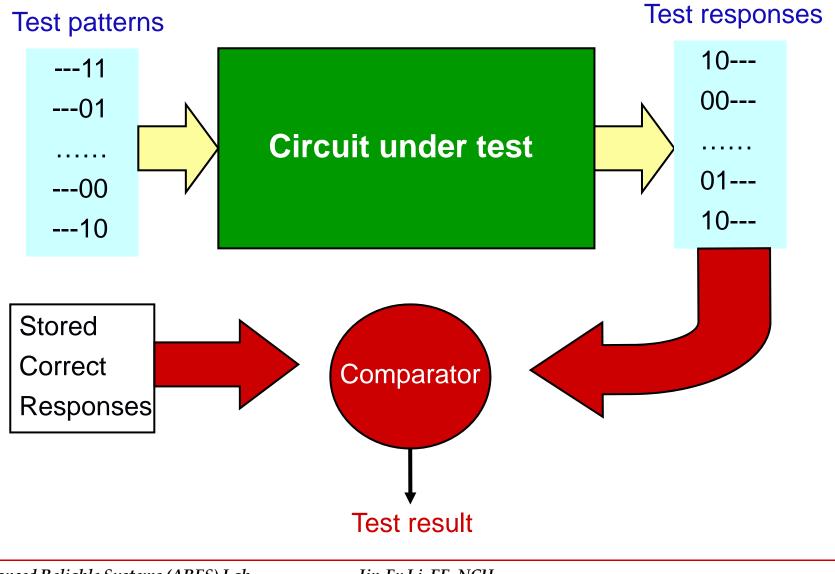

#### **How to Test Chips?**

### **Cost of Test**

- Design for testability (DFT)

- Chip area overhead and yield reduction

- Performance overhead

- □ Software processes of test

- Test generation and fault simulation

- Test programming and debugging

- Manufacturing test

- Automatic test equipment (ATE) capital cost

- Test center operational cost

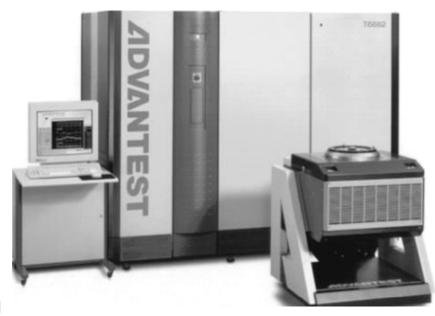

### **ADVENTEST Model T6682 ATE**

Consists of

- Powerful computer

- Powerful 32-bit digital signal processor (DSP) for analog testing

- Probe head: actually touches the bare dies or packaged chips to perform fault detection experiments

- Probe card: contains electronics to measure chip pin or pad

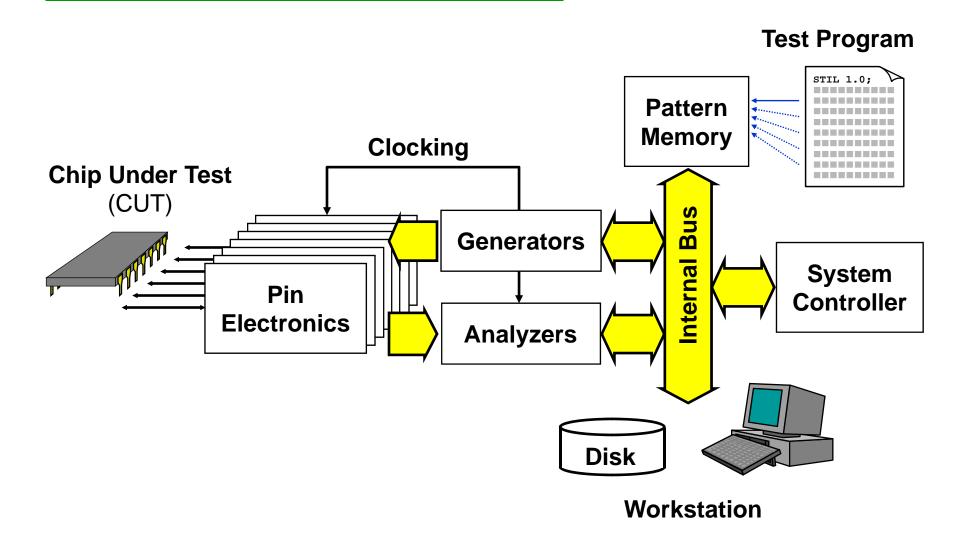

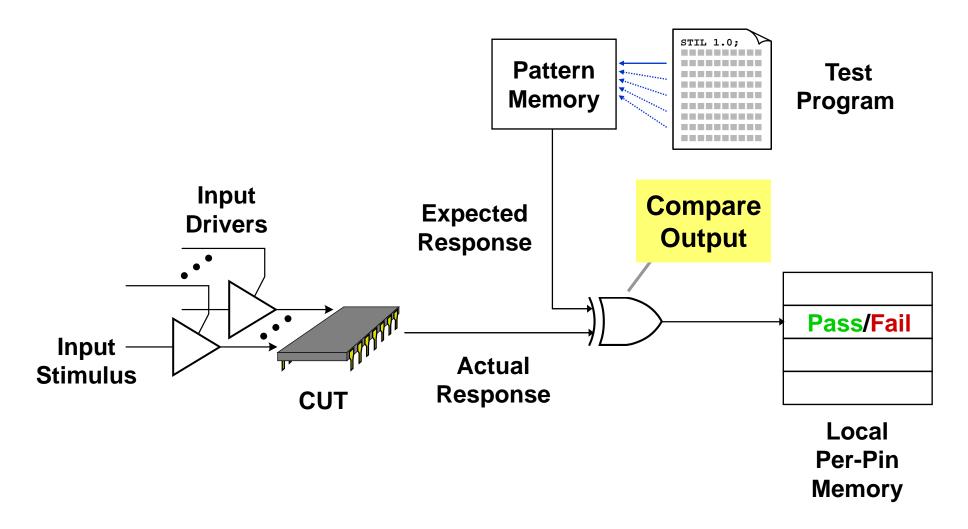

#### **Internal Structure of the ATE**

Source: H.-J. Huang, CIC

#### **ATE Test Operation**

Source: H.-J. Huang, CIC

#### Characterization testing

- A.k.s. design debug or verification testing

- Performed on a new design before it is sent to production

- Verify whether the design is correct and the device will meet all specifications

- Functional tests and comprehensive AC and DC measurements are made

- A characterization test determines the exact limits of device operation values

- DC Parameter tests

- Measure steady-state electrical characteristics

- For example, threshold test

- $\Box$  0<V<sub>OL</sub><V<sub>IL</sub>

- $\Box$  V<sub>IH</sub><V<sub>OH</sub><V<sub>CC</sub>

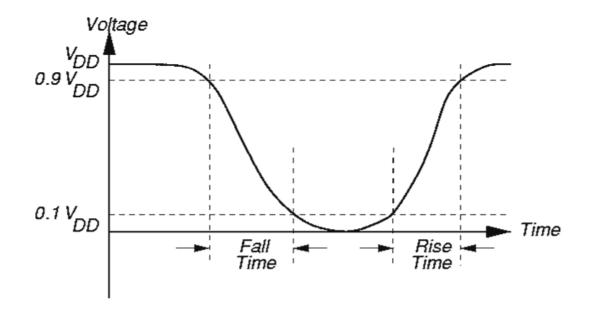

#### □ AC parametric tests

- Measure transient electronic characteristics

- For example:

□ Rise time & fall time tests

#### Production testing

- Every fabricated chip is subjected to production tests

- The test patterns may not cover all possible functions and data patterns but must have a high fault coverage of modeled faults

- The main driver is cost, since every device must be tested. Test time must be absolutely minimized

- Only a go/no-go decision is made

- Test whether some device-under-test parameters are met to the device specifications under normal operating conditions

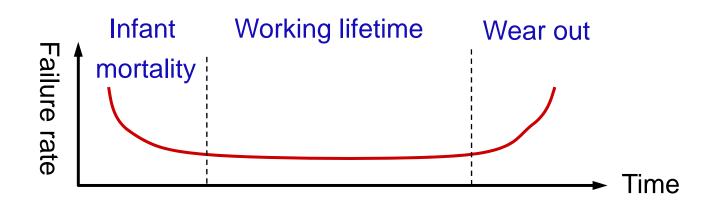

- Burn-In testing

- Ensure reliability of tested devices by testing

- Detect the devices with potential failures

- The potential failures can be accelerated at elevated temperatures

- The devices with infant mortality failures may be screened out by a short-term burn-in test in an accelerate

- □ Failure rate versus product lifetime (*bathtub curve*)

### **Testing Economics**

- Chips must be tested before they are assembled onto PCBs, which, in turn, must be tested before they are assembled into systems

- □ The rule of ten

- If a chip fault is not detected by chip testing, then finding the fault costs 10 times as much at the PCB level as at the chip level

- Similarly, if a board fault is not found by PCB testing, then finding the fault costs 10 times as much at the system level as at the board level

- Some claim that the rule of ten should be renamed the rule of twenty

Chips, boards, and systems are more complex

# **VLSI Chip Yield**

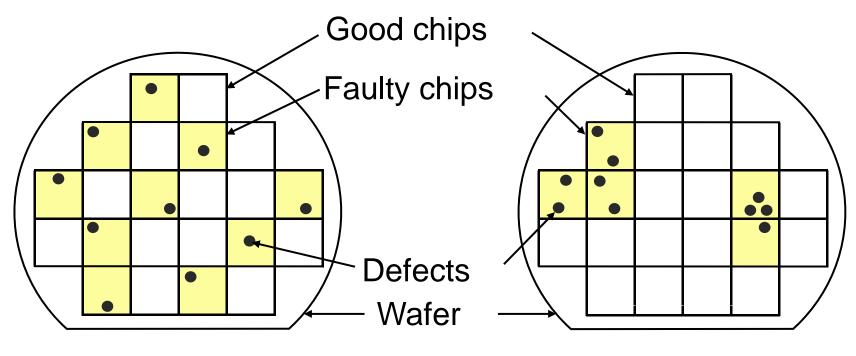

- A manufacturing defect is a finite chip area with electrically malfunctioning circuitry caused by errors in the fabrication process

- A chip with no manufacturing defect is called a good chip

- Fraction (or percentage) of good chips produced in a manufacturing process is called the *yield*. Yield is denoted by symbol Y

- Cost of a chip

Cost of fabricating and testing a wafer

Yield x Number of chip sites on the wafer

### **VLSI Chip Yield**

Wafer yield = 12/22 = 0.55

Wafer yield = 17/22 = 0.77

### Fault Coverage & Defect Level

#### □ Fault coverage (FC)

- The measure of the ability of a test (a collection of test patterns) to detect a given faults that may occur on the device under test

- FC=#(detected faults)/#(possible faults)

- Defect level (DL)

- The ratio of faulty chips among the chips that pass tests

- DL is measured as *defects per million* (DPM)

- DL is a measure of the effectiveness of tests

- DL is a quantitative measure of the manufactured product quality. For commercial VLSI chips a DL greater than 500 DPM is considered unacceptable

DL =

$$1 - Y^{(1-FC)}$$

and  $0 < DL \le 1 - Y$

# **Defect Level & Quality Level**

□ For example, required FC for DL=200 DPM

| Y(%)  | 10     | 50    | 90   | 95   | 99 |

|-------|--------|-------|------|------|----|

| FC(%) | 99.991 | 99.97 | 99.8 | 99.6 | 98 |

- □ Quality level (QL)

- The fraction of good parts among the parts that pass all the tests and are shipped

•

$$QL = 1 - DL = Y^{(1-FC)}$$

and  $0 \le QL \le 1$

Consequently, fault coverage affects the quality level

## Outline

#### Basics

- □ Fault Modeling

- Design-for-Testability

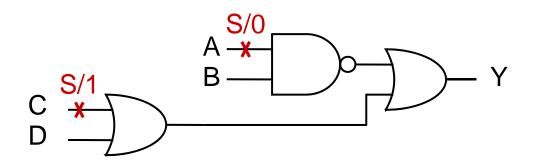

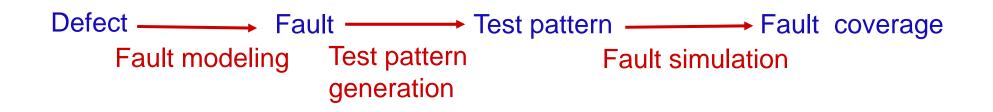

## **Test Process**

#### □ The testing problem

- Given a set of faults in the circuit under test (or device under test), how do we obtain a certain (small) number of test patterns which guarantees a certain (high) fault coverage?

- Test process

- What faults to test? (*fault modeling*)

- How are test pattern obtained? (*test pattern* generation)

- How is test quality (fault coverage) measured? (*fault simulation*)?

- How are test vectors applied and results evaluated? (ATE/BIST)

## **Defect Categories**

- Defect categories

- Random defects, which are independent of designs and processes

- Systematic defects, which depend on designs and processes used for manufacturing

- For example, random defects might be caused by random particles scattered on a wafer during manufacturing

A resistive open defect [Source: Cadence]

# Logical Fault Models

- Systematic defects might be caused by process variations, signal integrity, and design integrity issues.

- It is possible both random and systematic defects could happen on a single die

- With the continuous shrinking of feature sizes, somewhere below the 180nm technology node, system defects have a larger impact on yield than random defects

#### Logical faults

Logical faults represent the physical defects on the behaviors of the systems

# Why Model Faults

- I/O function tests inadequate for manufacturing (functionality versus component and interconnection testing)

- Real defects (often mechanical) too numerous and often not analyzable

- □ A fault model identifies targets for testing

- □ A fault model makes analysis possible

- Effectiveness measurable by experiments

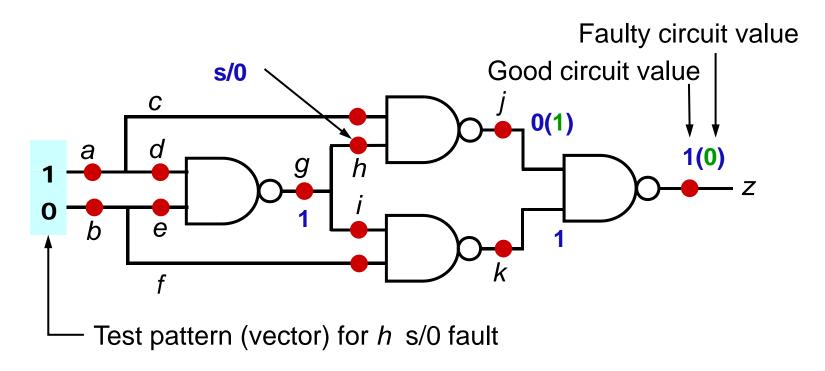

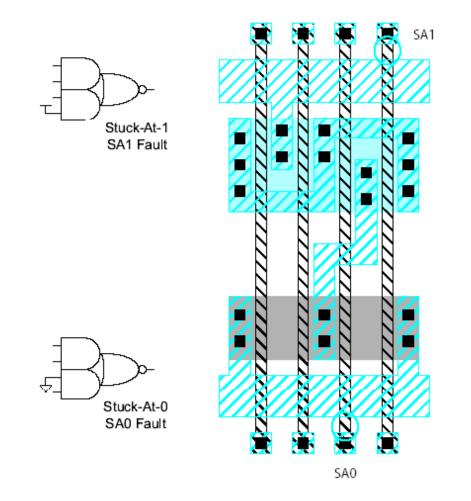

# Single Stuck-At Fault

- Single (line) stuck-at fault

- The given line has a constant value (0/1) independent of other signal values in the circuit

- Properties

- Only one line is faulty

- The faulty line is permanently set to 0 or 1

- The fault can be at an input or output of a gate

- Simple logical model is independent of technology details

- It reduces the complexity of fault-detection algorithms

- One stuck-at fault can model more than one kind of defect

# Single Stuck-At Fault Example

□ A circuit with single stuck-at fault

# Number of Single Stuck-At Faults

- Number of fault sites in a Boolean gate circuit

- #PI + #gates + #(fanout branches)

- Example: XOR circuit has 12 fault sites (•) and 24 single stuck-at faults

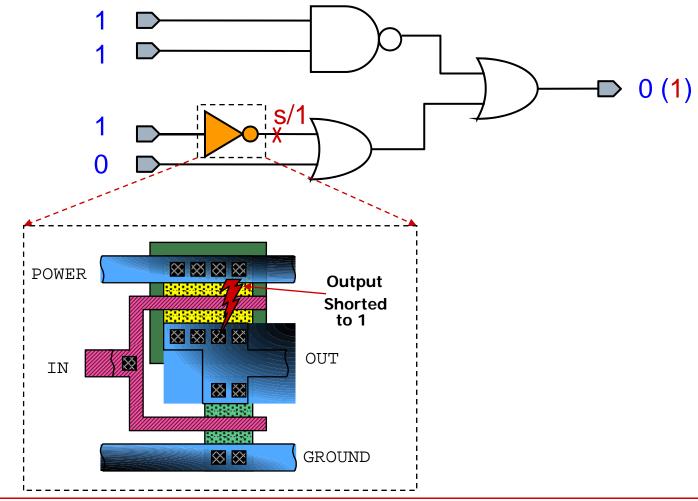

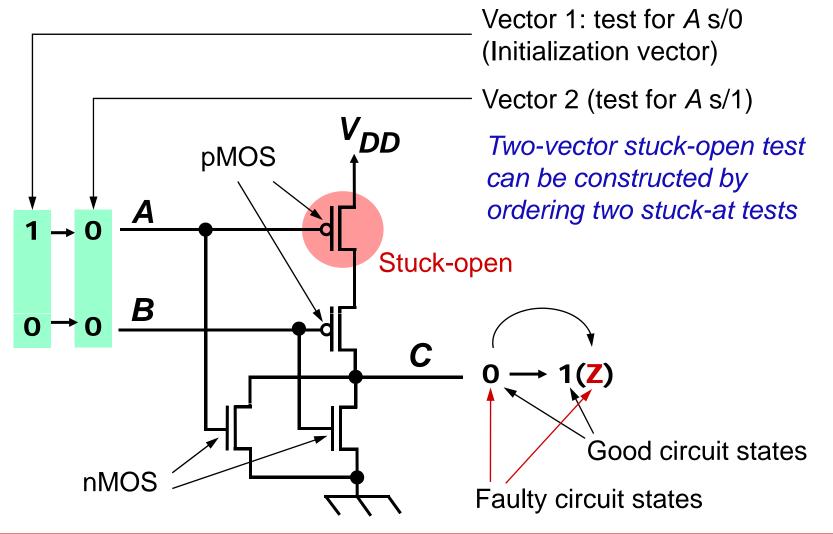

# **Transistor Faults**

- MOS transistor is considered an ideal switch and two types of faults are modeled

- Stuck-open -- a single transistor is permanently stuck in the open state

- □ Turn the circuit into a sequential one

- Need a sequence of at least 2 tests to detect a single fault

- Unique to CMOS circuits

- Stuck-on -- a single transistor is permanently shorted irrespective of its gate voltage

- Detection of a stuck-open fault requires two vectors

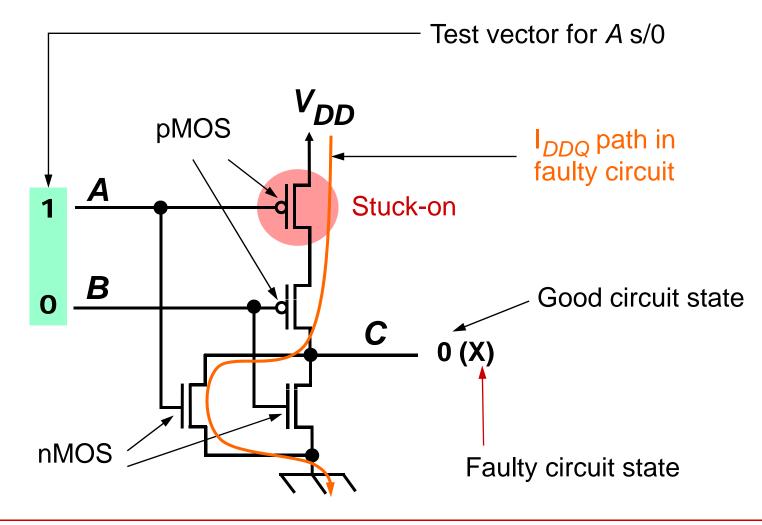

- Detection of a stuck-short fault requires the measurement of quiescent current (I<sub>DDQ</sub>)

Advanced Reliable Systems (ARES) Lab.

# Transistor Stuck-Open Fault

#### Example:

# Test Stuck-On Fault Using I DDQ

#### Example:

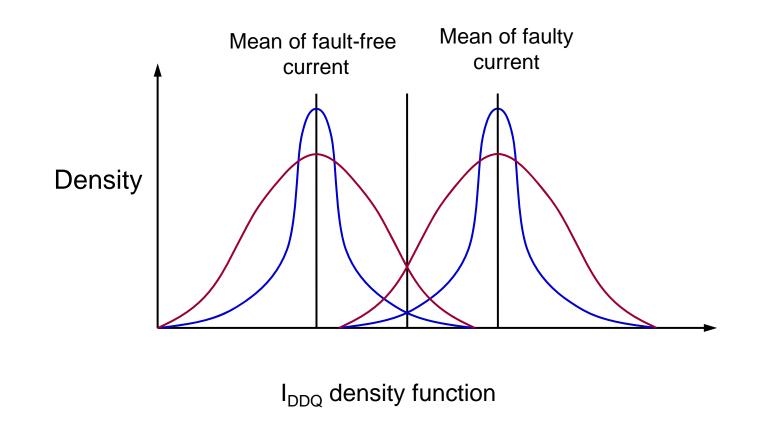

# I DDQ Test in Nano-scale Era

Major problem: may results in unacceptable yield loss

## Test & Test Set

- $\Box$  A *test* for a fault  $\alpha$  in a circuit *C* is an input combination for which the output(s) of *C* is different when  $\alpha$  is present than when it is not.

- A.k.a. test pattern or test vector

- X detect  $\alpha$  then  $f(X) \oplus f_{\alpha}(X) = 1$

- □ A *test set* for a class of faults *A* is a set of tests *T* such that  $\forall \alpha \in A, \exists t \in T \text{ and } t$  detects  $\alpha$

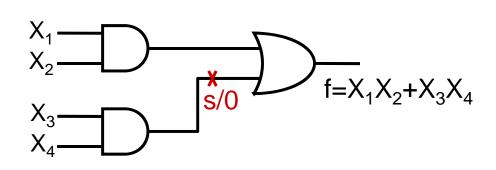

- The test set for a fault  $\alpha$  is  $T_{\alpha} = f \oplus f_{\alpha}$

- For example,

$$\begin{split} T_{\alpha} &= f \oplus f_{\alpha} \\ &= (X_1 X_2 + X_3 X_4) \oplus X_1 X_2 \\ &= \overline{X_1} X_3 X_4 + \overline{X_2} X_3 X_4 \\ &= \{0011, 0111, 1011\} \end{split}$$

# **Testing & Diagnosis**

- Testing is a process which includes test pattern generation, test pattern application, and output evaluation.

- Fault detection tells whether a circuit is fault-free or not

- Fault location provides the location of the detected fault

- Fault diagnosis provides the location and the type of the detected fault

- The input X distinguishes a fault  $\alpha$  from another fault  $\beta$  iff  $f_{\alpha}(X) \neq f_{\beta}(X)$ , i.e.,  $f_{\alpha}(X) \oplus f_{\beta}(X) = 1$

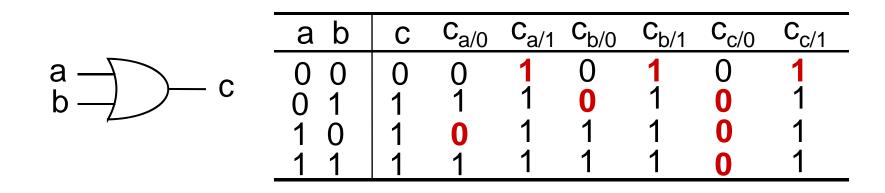

# **Testing & Diagnosis**

#### Example:

- $\hfill\Box$   $C_{a/0}$  and  $C_{c/0}$  are detected by the test pattern (1,0)

- $\Box$  If we apply two test patterns: (1,0) & (0, 1)

- Two corresponding outputs are faulty  $\rightarrow C_{c/0}$

- Only the output with respect to the input (1,0) is faulty  $\rightarrow C_{a/0}$

## Outline

- Basics

- □ Fault Modeling

- Design-for-Testability (Source: Prof. David Harris)

## **Stuck-At Faults**

#### □ How does a chip fail?

- Usually failures are shorts between two conductors or opens in a conductor

- This can cause very complicated behavior

- □ A simpler model: *Stuck-At*

- Assume all failures cause nodes to be "stuck-at" 0 or 1, i.e. shorted to GND or V<sub>DD</sub>

- Not quite true, but works well in practice

### **Examples**

# **Observability & Controllability**

- Observability: ease of observing a node by watching external output pins of the chip

- Controllability: ease of forcing a node to 0 or 1 by driving input pins of the chip

- Combinational logic is usually easy to observe and control

- □ Finite state machines can be very difficult, requiring many cycles to enter desired state

- Especially if state transition diagram is not known to the test engineer

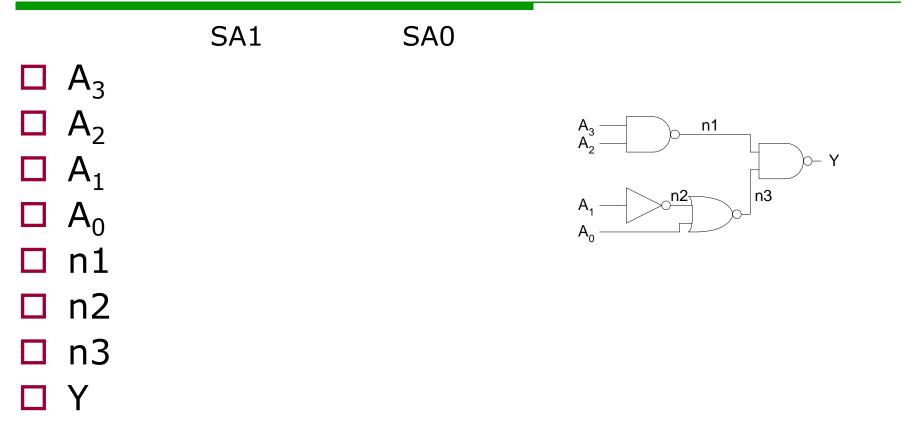

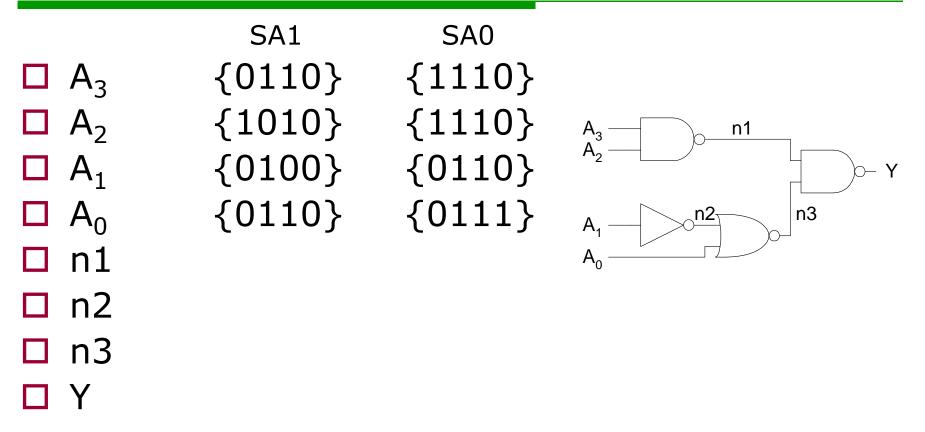

## **Test Pattern Generation**

- Manufacturing test ideally would check every node in the circuit to prove it is not stuck.

- Apply the smallest sequence of test vectors necessary to prove each node is not stuck.

- Good observability and controllability reduces number of test vectors required for manufacturing test.

- Reduces the cost of testing

- Motivates design-for-test

|                          | SA1        | SA0        |                   |

|--------------------------|------------|------------|-------------------|

| $\square$ A <sub>3</sub> | $\{0110\}$ | $\{1110\}$ |                   |

| $\square$ A <sub>2</sub> |            |            | A <sub>3</sub> n1 |

| $\square$ A <sub>1</sub> |            |            | $A_2 - V$         |

| $\square$ A <sub>0</sub> |            |            | $A_1 - n2$ $n3$   |

| 🗖 n1                     |            |            | $A_0$             |

| 🗖 n2                     |            |            |                   |

| 🗖 n3                     |            |            |                   |

| Ο Υ                      |            |            |                   |

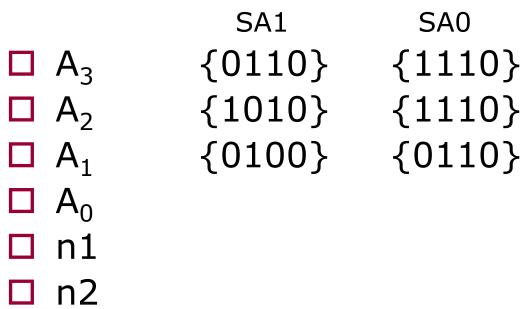

|                       | SA1        | SA0        |                  |

|-----------------------|------------|------------|------------------|

| $\Box A_3$            | $\{0110\}$ | $\{1110\}$ |                  |

| $\square A_2$         | $\{1010\}$ | $\{1110\}$ | A <sub>3</sub>   |

| $\Box$ A <sub>1</sub> |            |            | A <sub>2</sub> — |

| $\square A_0$         |            |            | A <sub>1</sub>   |

| 🗖 n1                  |            |            | A <sub>0</sub>   |

| 🗖 n2                  |            |            |                  |

| 🗖 n3                  |            |            |                  |

| ΠY                    |            |            |                  |

n1

)o- Y

n3

□ n2 □ n3 □ Y

| $\begin{array}{c c} & A_3 \\ \hline & A_2 \\ \hline & A_1 \\ \hline & A_0 \\ \hline & n1 \\ \hline & n2 \\ \hline & n3 \end{array}$ | SA1<br>{0110}<br>{1010}<br>{0100}<br>{0110}<br>{1110} | SA0<br>{1110}<br>{1110}<br>{0110}<br>{0111}<br>{0110} | $A_3 \xrightarrow{n1} \xrightarrow{r} Y$ |

|-------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|-------------------------------------------------------|------------------------------------------|

| □ n2<br>□ n3<br>□ Y                                                                                                                 |                                                       |                                                       |                                          |

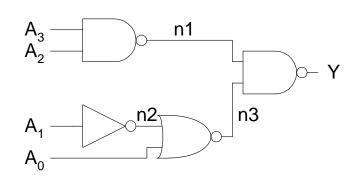

|                          | SA1        | SA0        |                   |

|--------------------------|------------|------------|-------------------|

| $\Box$ A <sub>3</sub>    | $\{0110\}$ | $\{1110\}$ |                   |

| $\square$ A <sub>2</sub> | $\{1010\}$ | $\{1110\}$ | A <sub>3</sub> n1 |

| $\square$ A <sub>1</sub> | $\{0100\}$ | $\{0110\}$ | $A_2 - V$         |

| $\square$ A <sub>0</sub> | $\{0110\}$ | $\{0111\}$ | A <sub>1</sub> n3 |

| 🗖 n1                     | $\{1110\}$ | $\{0110\}$ | A <sub>0</sub>    |

| 🗖 n2                     | $\{0110\}$ | $\{0100\}$ |                   |

| 🗖 n3                     |            |            |                   |

| <b>V</b>                 |            |            |                   |

|                       | SA1        | SA0        |

|-----------------------|------------|------------|

| $\Box A_3$            | $\{0110\}$ | $\{1110\}$ |

| $\Box A_2$            | $\{1010\}$ | $\{1110\}$ |

| $\Box$ A <sub>1</sub> | $\{0100\}$ | $\{0110\}$ |

| $\Box A_0$            | $\{0110\}$ | $\{0111\}$ |

| 🛛 n1                  | $\{1110\}$ | $\{0110\}$ |

| 🗆 n2                  | $\{0110\}$ | $\{0100\}$ |

| 🗆 n3                  | $\{0101\}$ | $\{0110\}$ |

| ΟY                    |            |            |

|                          | SA1        | SA0        |                                                      |

|--------------------------|------------|------------|------------------------------------------------------|

| $\Box$ A <sub>3</sub>    | $\{0110\}$ | $\{1110\}$ |                                                      |

| $\square$ A <sub>2</sub> | $\{1010\}$ | $\{1110\}$ |                                                      |

| $\Box$ A <sub>1</sub>    | $\{0100\}$ | $\{0110\}$ | $A_3 \longrightarrow n1$<br>$A_2 \longrightarrow -Y$ |

| $\Box A_0$               | $\{0110\}$ | $\{0111\}$ | n2 n3                                                |

| 🗖 n1                     | $\{1110\}$ | $\{0110\}$ | $A_1 \longrightarrow A_2 \longrightarrow A_1$        |

| 🗖 n2                     | $\{0110\}$ | $\{0100\}$ | 0                                                    |

| 🗖 n3                     | $\{0101\}$ | $\{0110\}$ |                                                      |

| ΓY                       | $\{0110\}$ | $\{1110\}$ |                                                      |

Minimum set: {0100, 0101, 0110, 0111, 1010, 1110}

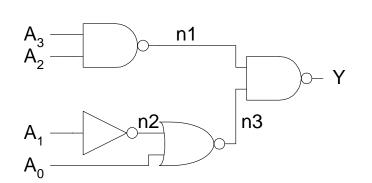

## **Design for Test**

- Design the chip to increase observability and controllability

- If each register could be observed and controlled, test problem reduces to testing combinational logic between registers.

- Better yet, logic blocks could enter test mode where they generate test patterns and report the results automatically.

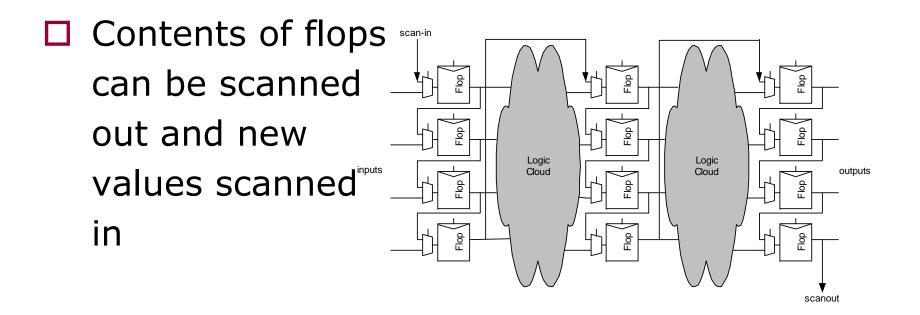

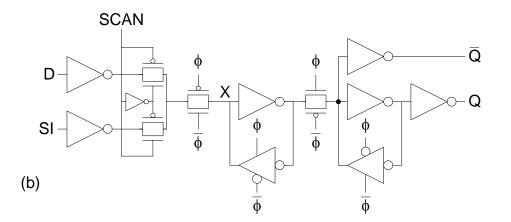

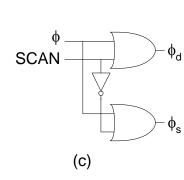

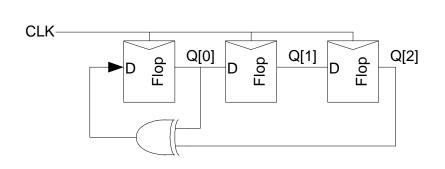

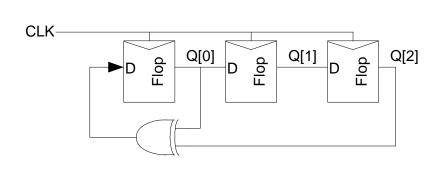

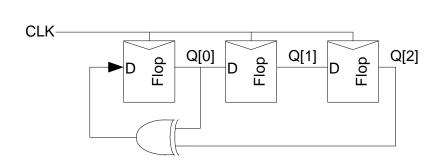

#### Scan

### Scannable Flip-flops

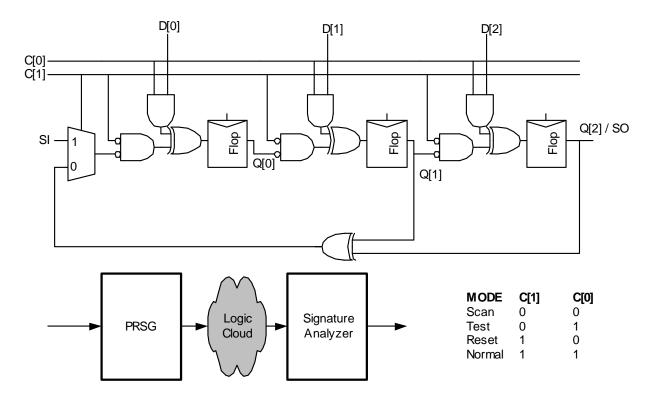

## **Built-in Self-test**

Built-in self-test lets blocks test themselves

- Generate pseudo-random inputs to comb. logic

- Combine outputs into a syndrome

- With high probability, block is fault-free if it produces the expected syndrome

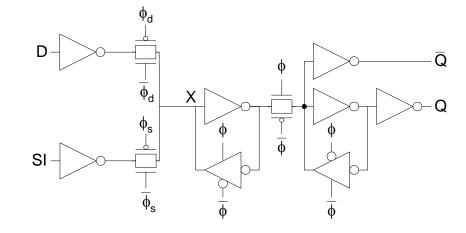

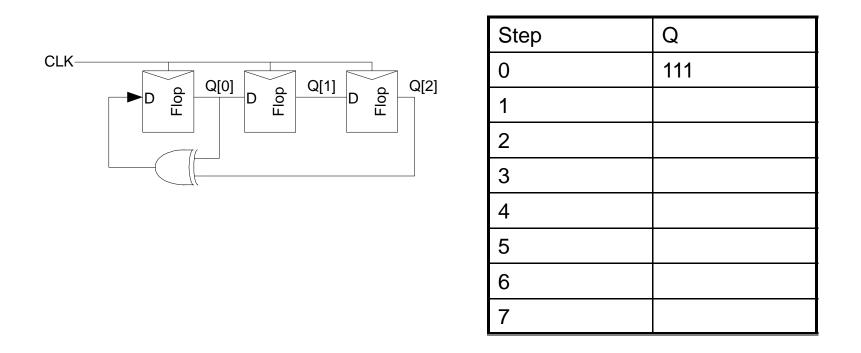

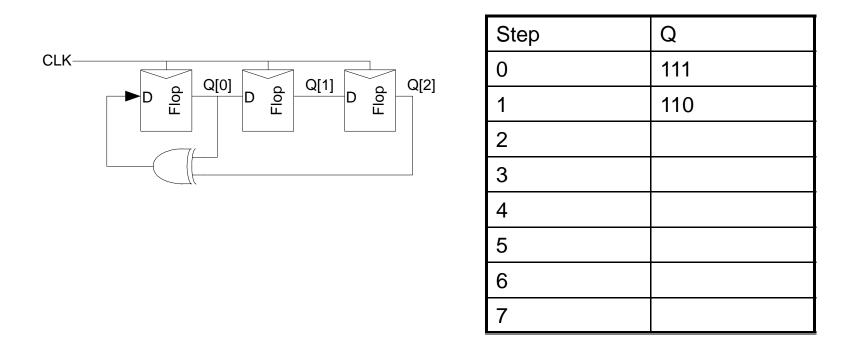

- Shift register with input taken from XOR of state

- Pseudo-Random Sequence Generator

- Shift register with input taken from XOR of state

- Pseudo-Random Sequence Generator

- Shift register with input taken from XOR of state

- Pseudo-Random Sequence Generator

- Shift register with input taken from XOR of state

- Pseudo-Random Sequence Generator

| Step | Q   |

|------|-----|

| 0    | 111 |

| 1    | 110 |

| 2    | 101 |

| 3    | 010 |

| 4    |     |

| 5    |     |

| 6    |     |

| 7    |     |

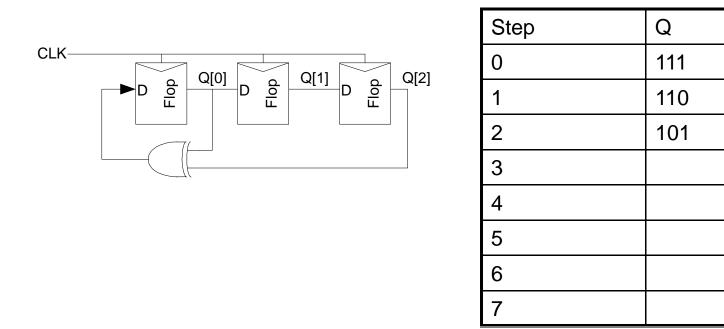

- Shift register with input taken from XOR of state

- Pseudo-Random Sequence Generator

| Step | Q   |

|------|-----|

| 0    | 111 |

| 1    | 110 |

| 2    | 101 |

| 3    | 010 |

| 4    | 100 |

| 5    |     |

| 6    |     |

| 7    |     |

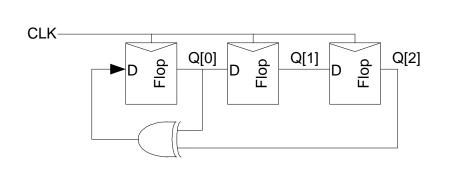

- Shift register with input taken from XOR of state

- Pseudo-Random Sequence Generator

| Step | Q   |

|------|-----|

| 0    | 111 |

| 1    | 110 |

| 2    | 101 |

| 3    | 010 |

| 4    | 100 |

| 5    | 001 |

| 6    |     |

| 7    |     |

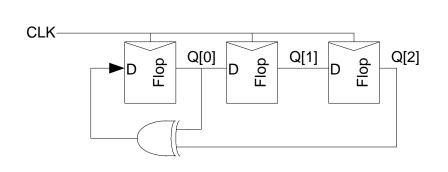

- Shift register with input taken from XOR of state

- Pseudo-Random Sequence Generator

| Step | Q   |

|------|-----|

| 0    | 111 |

| 1    | 110 |

| 2    | 101 |

| 3    | 010 |

| 4    | 100 |

| 5    | 001 |

| 6    | 011 |

| 7    |     |

- Shift register with input taken from XOR of state

- Pseudo-Random Sequence Generator

| Step | Q             |

|------|---------------|

| 0    | 111           |

| 1    | 110           |

| 2    | 101           |

| 3    | 010           |

| 4    | 100           |

| 5    | 001           |

| 6    | 011           |

| 7    | 111 (repeats) |

## BILBO

#### Built-in Logic Block Observer

Combine scan with PRSG & signature analysis

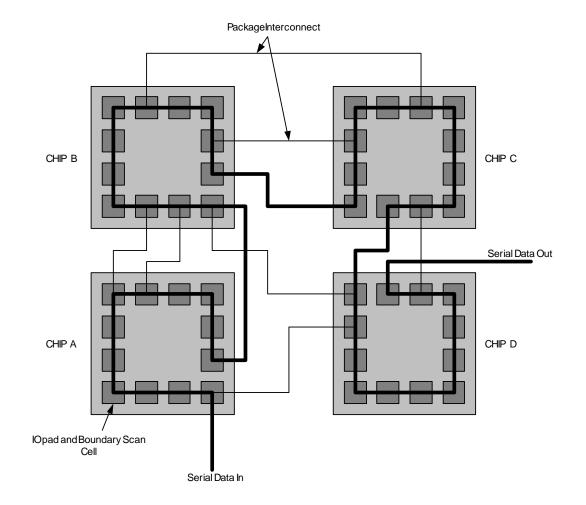

## **Boundary Scan**

- Testing boards is also difficult

- Need to verify solder joints are good

- Drive a pin to 0, then to 1

- Check that all connected pins get the values

- Through-hold boards used "bed of nails"

- SMT and BGA boards cannot easily contact pins

- Build capability of observing and controlling pins into each chip to make board test easier

### **Boundary Scan Example**

## **Boundary Scan Interface**

#### □ Boundary scan is accessed through five pins

- TCK: test clock

- TMS: test mode select

- TDI: test data in

- TDO: test data out

- TRST\*: test reset (optional)

- Chips with internal scan chains can access the chains through boundary scan for unified test strategy.

# Summary

Think about testing from the beginning

- Simulate as you go

- Plan for test after fabrication

- "If you don't test it, it won't work! (Guaranteed)"