# Synthesizable Coding of Verilog

REF:

•Verilog Training Manual, CIC, July, 2008

•Reuse Methodology Manual – For System-ON-A-Chip Design, Third Edition 2002

•Logic Synthesis with Design Complier, CIC , July, 2008

#### Speaker: Y. –X. Chen

Nov. 2012

Advanced Reliable Systems (ARES) Lab.

### 11/21

- □ 課程主題: Synthesizable Verilog & Coding

- □ 學習目標

- Synthesizable coding style in Verilog

- Syntax check with nLint

- □ LAB1 簡介-撰寫 simple 8-bit microprocessor之 Verilog code

- 步驟一:RTL coding並使用nLint確定為可合成之code

- 步驟二:使用修正好的RTL netlist跑simulation,並觀察波型

### Outline

- Basic of Logic Synthesis Concept

- Basic Concept of Verilog HDL

- Synthesizable Verilog

- □ LAB 1-1: Design Rule Check with nLint

- Tips for Verilog Design

- □ LAB 1-2: RTL Simulation

### **Basic Concept of the Synthesis**

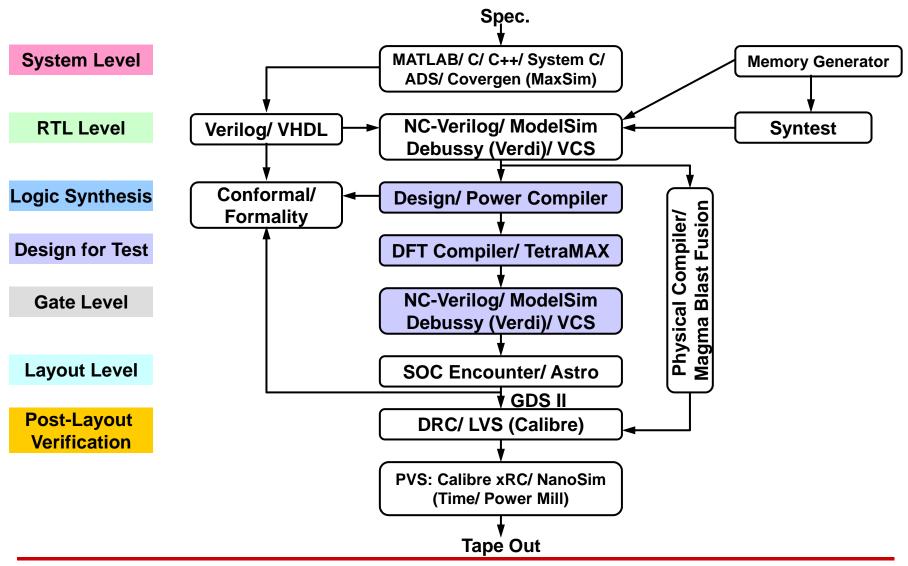

### **Cell-Based Design Flow**

Advanced Reliable Systems (ARES) Lab.

### What is Synthesis

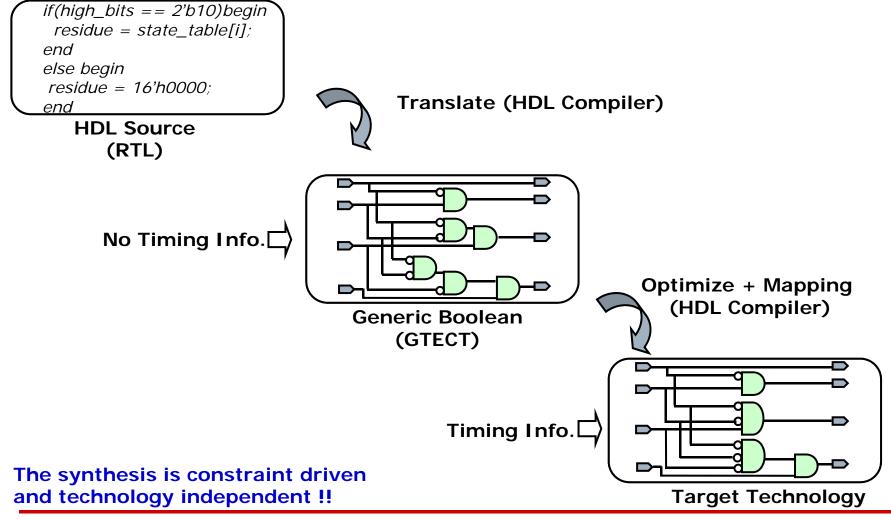

Synthesis = translation + optimization + mapping

Advanced Reliable Systems (ARES) Lab.

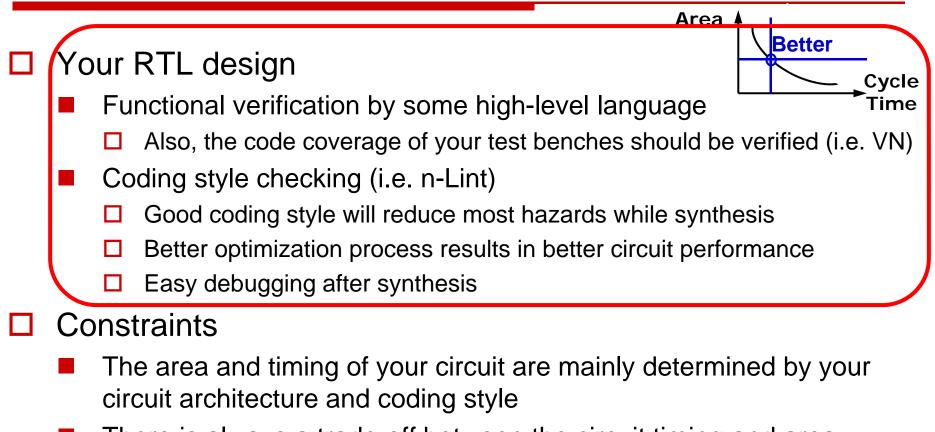

### **Notice Before Synthesis**

- There is always a trade-off between the circuit timing and area

- In fact, a super tight timing constraint may be worked while synthesis, but failed in the Place & Route (P&R) procedure

### **Basic Concept of Verilog HDL**

# **Verilog Model**

#### Key features of Verilog

- Supports various level of abstraction

- Switch level model or transistor level model

- Gate level model

- Data flow model or register transfer model

- Behavioral model

# **Register Transfer Level (RTL)**

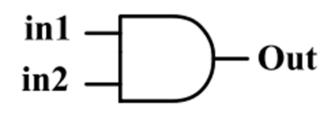

//BEH\_AND2

module AND2(in1,in2,Out)

input in1,in2;

output Out;

reg Out;

always@(in1 or in2) begin Out=in1 & in2; end endmodule

### **Gate Level Model**

Model consists of basic logic

Ex. AND, NAND, OR, NOR, XOR, NOT, etc.

//GateAND2 module AND2(in1,in2,Out) input in1,in2; output Out;

and u1(Out,in1,in2); endmodule

# **Verilog Module**

#### module module\_name(port\_names); •Port declaration •Data type declaration •Task & function declaration •Module functionality or structure •Timing Specification endmodule

| /* This is sample c<br>The function is ALL                                        |                                                         |

|-----------------------------------------------------------------------------------|---------------------------------------------------------|

| */<br>module ALU(a,b,se<br>input [7:0] a,b;<br>output[7:0]out;<br>input [2:0]sel; | el,out);<br>//Data in<br>//Data out<br>//Control select |

| reg [7:0]out;<br>wire                                                             | // Control Select                                       |

| always@()begin<br><br>end                                                         |                                                         |

| <br>endmodule                                                                     |                                                         |

# Verilog Syntax

- Verilog consists of a series token

- Comment: //, /\* \*/

- operators: unary, binary, ternary

- □ A=~B;

- □ A=B&C;

- □ C=SEL?A:B;

- Numbers: size, unsized

- □ Sized: 4'b0010, 8'ha

- Identifiers: \$, #, etc.

- Keywords

# Verilog Syntax (Cont'd)

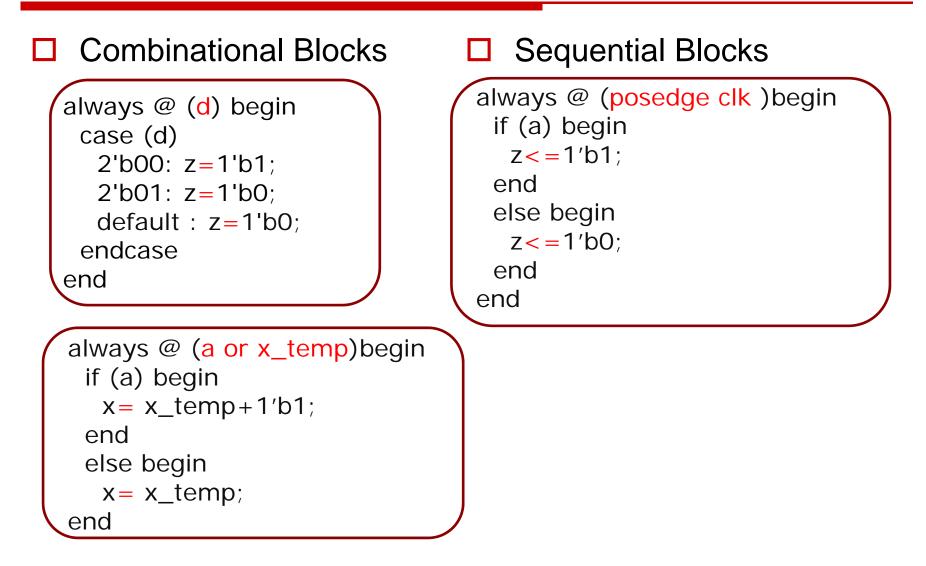

#### always@ statement

- Blocking

- Non-blocking

```

always @ (posedge clk) begin

x_temp<=x;

end

always @ (a or x_temp)begin

if (a) begin

x= x_temp+1'b1;

end

else begin

x= x_temp;

end</pre>

```

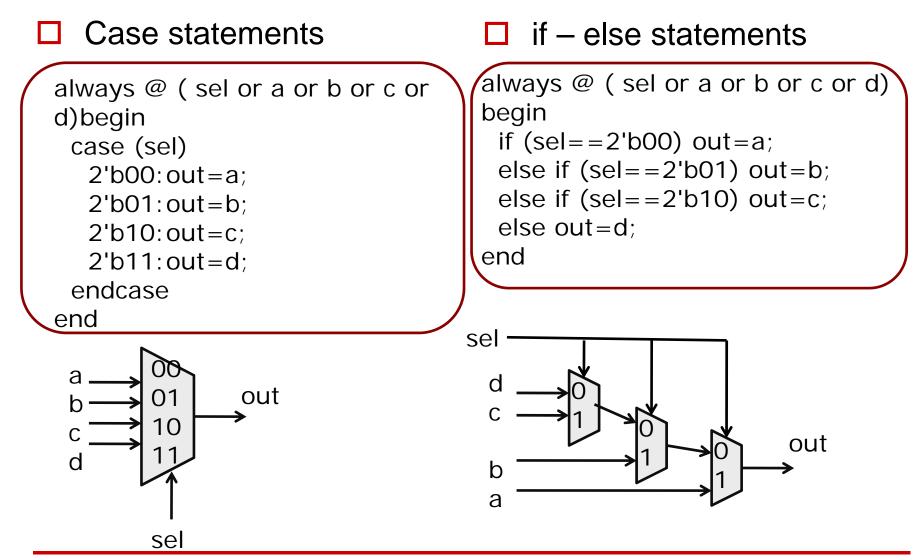

# Verilog Syntax (Cont'd)

- Case statement

- If-else statement

```

always @ (d) begin

case (d)

2'b00: z=1'b1;

2'b01: z=1'b0;

default : z=1'b0;

endcase

end

always @ (a or x_temp)begin

if (a) begin

x = x_temp + 1'b1;

end

else begin

x = x_temp;

end

```

### **Connection Manners**

### Synthesizable Verilog

### Importance of Coding Style

- Make sure your code is readable, modifiable, and reusable

- Good coding style helps to achieve better results in synthesis and simulation

### **Concept of Clocks and Reset**

### **Asynchronous and Synchronous Reset**

#### Synchronous reset

|     | nys@(posedge clock)begin<br>if (rst) begin |

|-----|--------------------------------------------|

|     | end                                        |

| end | •••                                        |

#### □ Asynchronous reset

always@(posedge clock or negedge reset) if (!rst) begin .... end ... end

Advanced Reliable Systems (ARES) Lab.

# Synthesizable Verilog

- Not all kinds of Verilog constructs can be synthesized

- Only a subset of Verilog constructs can be synthesized and the code containing only this subset is synthesizable

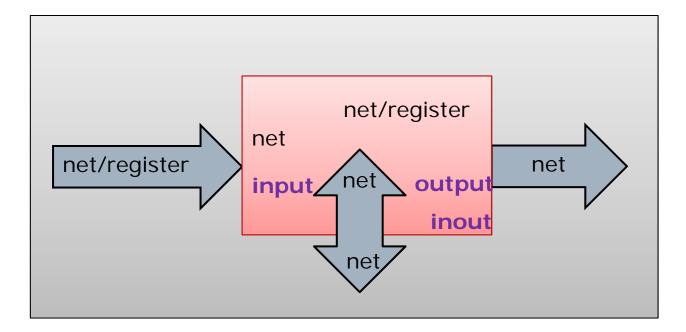

# Synthesizable Verilog (Cont')

- Verilog Basis

- parameter declarations

- wire, wand, wor declarations

- reg declarations

- input, output, inout

- continuous assignment

- module instructions

- gate instructions

- always blocks

- task statement

- function definitions

- for, while loop

- Synthesizable Verilog primitives cells

- and, or, not, nand, nor, xor, xnor

- bufif0, bufif1, notif0, notif1

fork

join

event

• Can not use for Synthesis

| ===                         | delay   |

|-----------------------------|---------|

| !==                         | Initial |

| / (division)<br>% (modulus) | repeat  |

|                             | forever |

|                             | wait    |

# Synthesizable Verilog (Cont')

#### Operators

- Concatenation ( { }, { { } } )

- Unary reduction  $(!, \sim, \&, |, \wedge)$

- 2's complement arithmetic (+, -, \*)

- Logic shift ( >>, << )

- Relational ( >, <, >=, <= )

- Equality ( ==, != )

- Binary bit-wise ( &, |, ^, ~^ )

- Logical ( &&, || )

- Conditional (?:)

#### Advanced Reliable Systems (ARES) Lab.

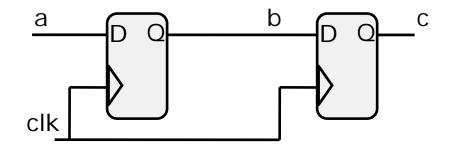

# **Coding for Synthesis**

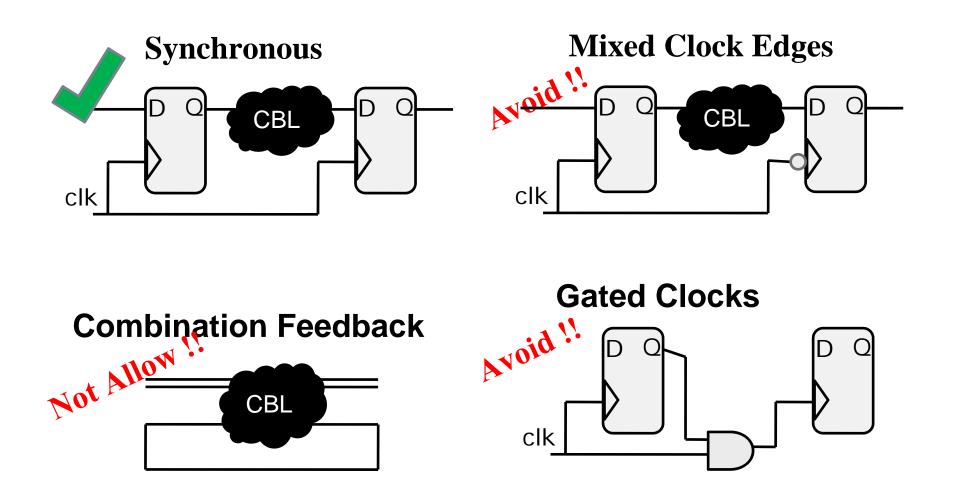

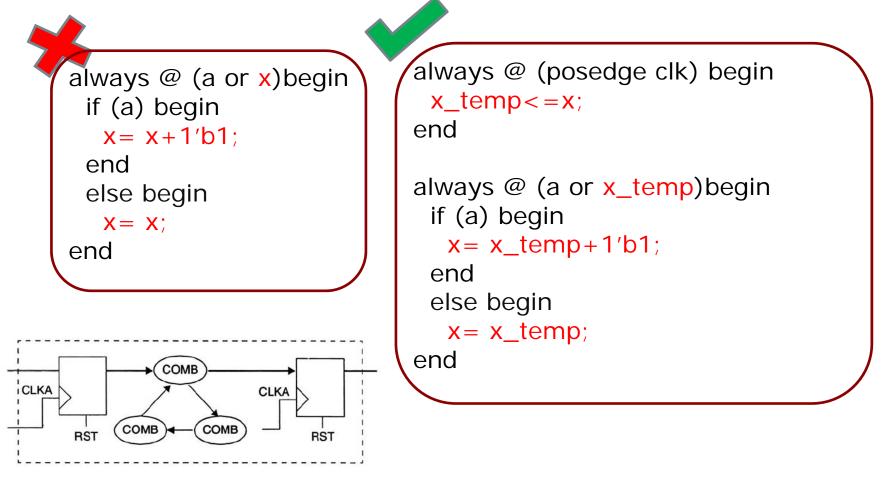

Avoid Combinational Feedback

Just like "a=c;"

Just like "shift register"

Advanced Reliable Systems (ARES) Lab.

#### □ Sensitivity List

Advanced Reliable Systems (ARES) Lab.

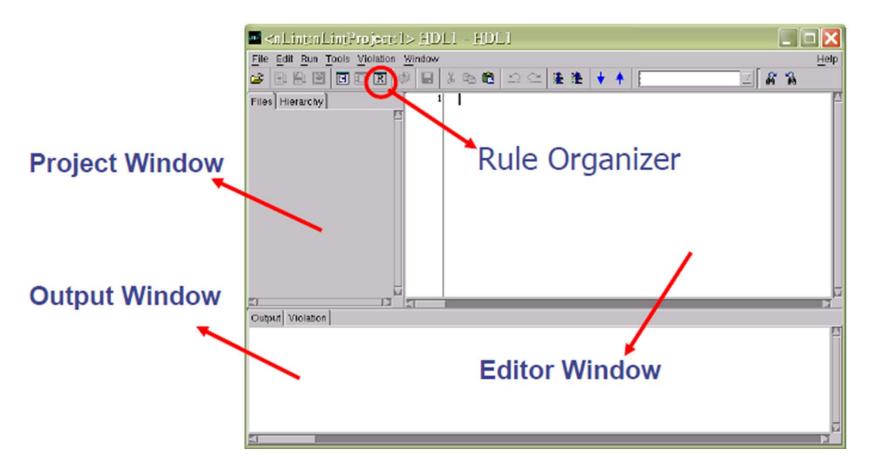

### Lab 1-1 Design Rule Check with nLint

### **Design Rule Check**

Use nLint tool (include by Debussy) and the Verilog Coding Guideline to check your design and modify parts of code to match the coding guidelines

#### □ Unix% <u>nLint –gui &</u>

# Load Verilog Code (1/2)

| # Import Design                                                     |                 |

|---------------------------------------------------------------------|-----------------|

| From Librar From File                                               |                 |

| Language: Verilog Virtual Top:                                      | Browse          |

| Default Directory:                                                  |                 |

| /home10/PHD/lyhsieh/System-Design-class/2008/nLint                  | Browse          |

| Design Files:                                                       |                 |

| vhome10/PHD/tyhsien/System-Design-class/2006/nLinVmytraffic_light.v | Delete          |

|                                                                     | Options         |

|                                                                     |                 |

|                                                                     |                 |

|                                                                     |                 |

| /home10/PHD/tyhsieh/System-Design-class/2006/nLinVmytraffic_light.v |                 |

| Cu /home10/PHD/tyhsieh/System-Design-     CunLintOB                 | Add             |

|                                                                     |                 |

| # ⊇ nLintDB                                                         | -               |

|                                                                     | 2               |

|                                                                     |                 |

|                                                                     |                 |

|                                                                     |                 |

|                                                                     |                 |

|                                                                     |                 |

|                                                                     |                 |

|                                                                     | Filter          |

|                                                                     | ≥v; ".slg; ".{⊠ |

|                                                                     |                 |

|                                                                     |                 |

| Compile after the design imported                                   |                 |

|                                                                     |                 |

| 3 Сок                                                               | Cancel          |

|                                                                     |                 |

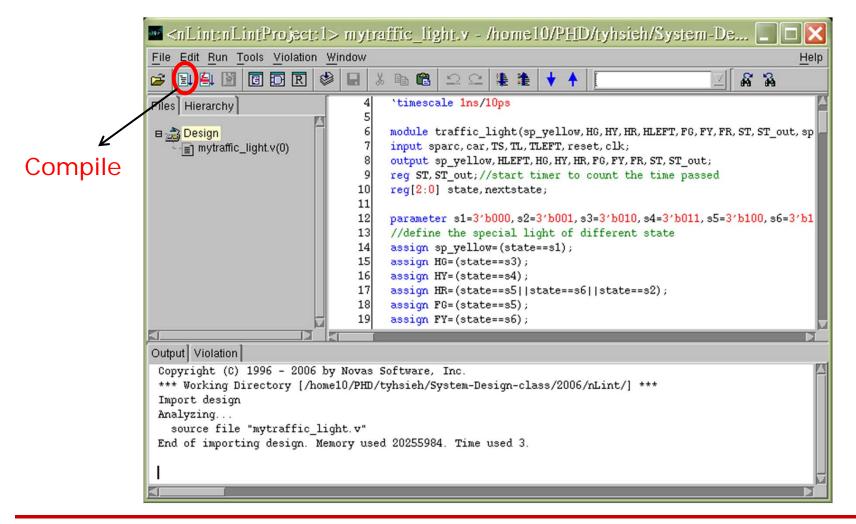

# Load Verilog Code (2/2)

| File Edit Run Tools Violation Window Help                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 🚅 🖹 🗐 🖸 🖸 🛛 🖉 👙 🖶 🙏 🛍 🗅 오 🎼 🌲 🛉 🛉 🚺 🖂 🖾 🛣                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Files Hierarchy 4 'timescale 1ns/10ps                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| <pre>module traffic_light(sp_yellow, HG, HY, HR, HLEFT, FG, FY, FR, ST, ST_out, sp<br/>input spare, car, TS, TL, TLEFT, reset, elk;<br/>output sp_yellow, HLEFT, HG, HY, HR, FG, FY, FR, ST, ST_out;<br/>reg ST, ST_out; //start timer to count the time passed<br/>reg[2:0] state, nextstate;<br/>parameter s1=3'b000, s2=3'b001, s3=3'b010, s4=3'b011, s5=3'b100, s6=3'b1<br/>//define the special light of different state<br/>scoign op_yellow-(states1);<br/>scoign HO-(states1);<br/>scoign HY-(states5  states6  states2];<br/>sssign FC=(state==s5);<br/>sssign FY=(state==s6);</pre> |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Output Violation<br>Copyright (C) 1995 - 2005 by Novae Software, Inc.<br>*** Vorking Directory [/home10/PHD/tyheich/System-Design-class/2006/nLint/] ***<br>Inport design<br>Analyzing<br>source file "nytraffic_light.v"<br>End of inporting design. Menory used 20255984. Time used 3.                                                                                                                                                                                                                                                                                                      |

Advanced Reliable Systems (ARES) Lab.

### **Run nLint Check**

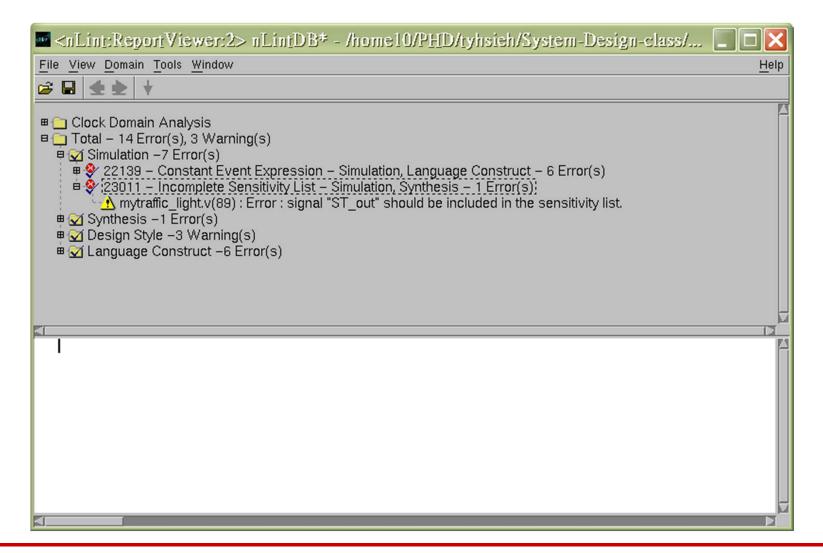

### nLint Check Result (1/2)

## nLint Check Results (2/2)

| 🖇 🗐 😫 📴 🖸 🖪 🔍 😫                                          | ( 🖬 😫                                      | 6 🗈 🛍                                                        | 294         | 逢 🕴      | +     | l. | 2 <b>A</b> A |  |

|----------------------------------------------------------|--------------------------------------------|--------------------------------------------------------------|-------------|----------|-------|----|--------------|--|

| iles Hierarchy                                           | 28                                         |                                                              | (state or n | extstate | e)    |    |              |  |

| A Dealar                                                 | 29<br>30                                   | begin                                                        |             | novt     | stata |    |              |  |

| B Besign                                                 | 30 st_o = ~(state == nextstate);<br>31 end |                                                              |             |          |       |    |              |  |

| traffic_light.v(5)                                       | 32                                         | 32                                                           |             |          |       |    |              |  |

|                                                          | 33                                         | 32<br>33                                                     |             |          |       |    |              |  |

|                                                          | 34<br>35                                   | 34 always @(posedge clock or posedge st) // counter          |             |          |       |    |              |  |

|                                                          | 35                                         | 35 begin                                                     |             |          |       |    |              |  |

|                                                          | 36                                         | 36 if (st)                                                   |             |          |       |    |              |  |

|                                                          | 20                                         | count = 0;                                                   |             |          |       |    |              |  |

|                                                          | 38                                         | <pre>38 else     count = count + 5'd1;</pre>                 |             |          |       |    |              |  |

|                                                          | 40                                         | 40 end                                                       |             |          |       |    |              |  |

|                                                          | 41                                         |                                                              |             |          |       |    |              |  |

|                                                          | 42                                         | 42 always &(posedge clock or posedge reset) //for next state |             |          |       |    |              |  |

| 1                                                        | 43                                         | 43 begin                                                     |             |          |       |    |              |  |

|                                                          | 1                                          |                                                              |             |          |       |    |              |  |

| utput Violation                                          |                                            |                                                              |             |          |       |    |              |  |

| Lint processing done.                                    |                                            |                                                              |             |          |       |    |              |  |

| Mon Nov 26 14:14:23 2007 E                               | nd of lin                                  | t.                                                           |             |          |       |    |              |  |

| Loading report DB file                                   |                                            |                                                              |             |          |       |    |              |  |

| Fotally 2 Error(s), 3 Warn<br>Loading report DB file, do |                                            | aded                                                         |             |          |       |    |              |  |

| soading report bb rife, do                               | 110 1                                      |                                                              |             |          |       |    |              |  |

| Total 2 Error(s), 3 Warnin                               | 1.5                                        |                                                              |             |          |       |    |              |  |

Advanced Reliable Systems (ARES) Lab.

#### Lab Time

### 11/28

- □ 課程主題: Synthesizable Verilog & Coding

- □ 學習目標

- Tips for Verilog Design

- RTL simulation

- Waveform viewer nWave / Debussy

- □ LAB1 簡介-撰寫 simple 8-bit microprocessor之 Verilog code 並模擬結果

- 步驟一:RTL coding並使用nLint確定為可合成之code

- 步驟二:使用修正好的RTL netlist跑simulation,並觀察波型

### Outline

- Basic of Logic Synthesis Concept

- Basic Concept of Verilog HDL

- Synthesizable Verilog

- □ LAB 1-1: Design Rule Check with nLint

- Tips for Verilog Design

- LAB 1-2: RTL Simulation

## **Tips for Verilog Design**

## **Pre-RTL Preparation Checklist**

- Communicate design issues with your team

- Naming conventions, revision control, directory tree and other design organizations

- □ Have a specification for your design

- Everyone should have a specification before they start coding

- Design partition

- Follow the specification's recommendations for partition

- Break the design into major function blocks

# **RTL Coding Style**

- Create a block level drawing of your design before you begin coding

- Draw a block diagram of the function and sub-function of your design

- Always think of the poor guy who has to read your RTL code

- Correlate "top to bottom in the RTL description" with left to right in block diagram

- Comments and headers

- □ Hierarchy design

## **Basic Coding Practices**

#### Naming Conventions

- Use lowercase letters for all signal names, and port names, versus uppercase letters for names of constants and user-defined types

- Use meaningful names

- For active low signals, end the signal name with an underscore followed by a lowercase character (e.g., rst\_ or rst\_n)

- Recommend using "bus[X:0]" for multi-bit signals

# **Basic Coding Practices (Cont')**

#### Include Headers in Source Files and Comments

| <pre>//ARES Lab., EE Dept., NCU, Jhongli, TAIWAN 320<br/>//http://ares.ncu.edu.tw/<br/>//Project : SOFT-ERROR-MITIGATION BIST &amp; DIAGNOSIS DATA COMPRESSION TECHNIQUES FOR HOY PROJECT<br/>//Module : bist<br/>//Adviser : Jin-Fu Li<br/>//Author : Tsu-Wei Tseng, Chun-Hsien Wu<br/>//E-mails : jfli@ee.ncu.edu.tw (Jin-Fu Li)<br/>// 92521013@cc.ncu.edu.tw (Tsu-Wei Tseng)<br/>// 93521039@cc.ncu.edu.tw (Chun-Hsien Wu)<br/>//Date : 2007/08<br/>//Abstract : Top module of the MBIST. This module consists of CTR, and Test Pattern Generator (TPG)</pre> |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <pre>module bist(<br/>Clk,<br/>rst,<br/>CSI,<br/>DO,<br/>hold,<br/>WEN_T,<br/>CS_T,<br/>OE_T,<br/>DI_T,<br/>ADDR_T,<br/>cmd_done,<br/>SYW,<br/>fail,<br/>test_done<br/>);<br/>//Parameter declarations</pre>                                                                                                                                                                                                                                                                                                                                                      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

Advanced Reliable Systems (ARES) Lab.

# **Basic Coding Practices (Cont')**

Indentation

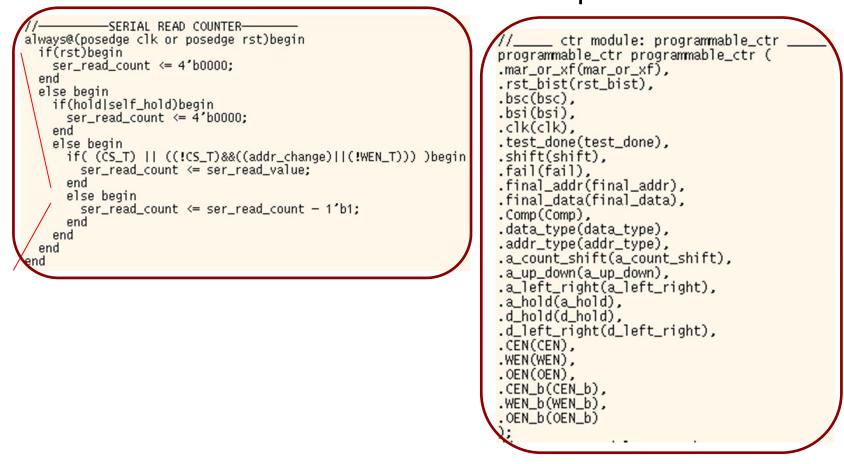

#### Port Maps and Generic Maps

# **Basic Coding Practices (Cont')**

#### Use Functions or Tasks

Which Instead of repeating the same sections of code

| task ra;                           |                        |

|------------------------------------|------------------------|

| begin                              |                        |

| WEB_T=1;//WEB=1:read               |                        |

| EOP[w+2:w]=3'b011;//EOP[w]=1: a    | and a                  |

|                                    | begin                  |

| FREE=CMD[w-1:0];                   | case(CMD[w+3:w])       |

| end<br>endtask                     | 4'b0000:begin // ra    |

| enucask                            | end_session=0;         |

| task rabar;                        | ra;                    |

| begin                              | end                    |

| WEB_T=1;//WEB=1:read               | 4'b0001:begin //wa'    |

| EOP[w+2:w]=3'b010;//EOP[w]=0: abar | end_session=0;         |

| DI_T=~CMD[w-1:0];                  | wabar:                 |

| FREE=~CMD[w-1:0];                  | end                    |

| end<br>endtask                     | 4'b0010:begin //ra'    |

| enucask                            | end_session=0;         |

| task wa:                           | rabar:                 |

| begin                              | end                    |

| WEB_T=0;//WEB=0:write              |                        |

| EOP[w+2:w]=3'b001;                 | 4'b0011:begin //wa     |

| <pre>DI_T=CMD[w-1:0];</pre>        | end_session=0;         |

| FREE=CMD[w-1:0];                   | wa;                    |

| end<br>endtask                     | end                    |

| enucask                            | 4'b0100:begin //ra wa' |

| task wabar;                        | end_session=1;         |

| begin                              | case(session_state)    |

| WEB_T=0;//WEB=0:write              | 4'b0000:ra;            |

| EOP[w+2:w]=3'b000;                 | 4'b0001:wabar;         |

| DI_T=~CMD[w-1:0];//Maybe wrong     | default:ra;            |

| FREE=~CMD[w-1:0];<br>end           | endcase                |

| endtask                            | end                    |

|                                    |                        |

Advanced Reliable Systems (ARES) Lab.

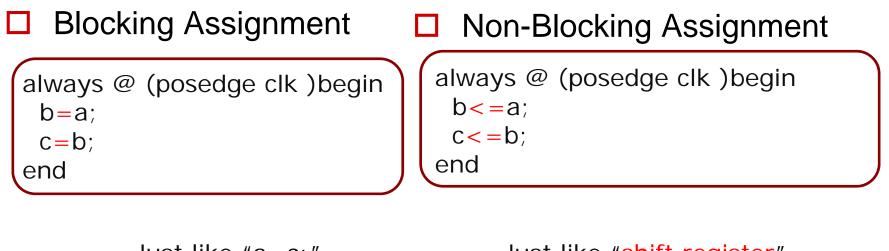

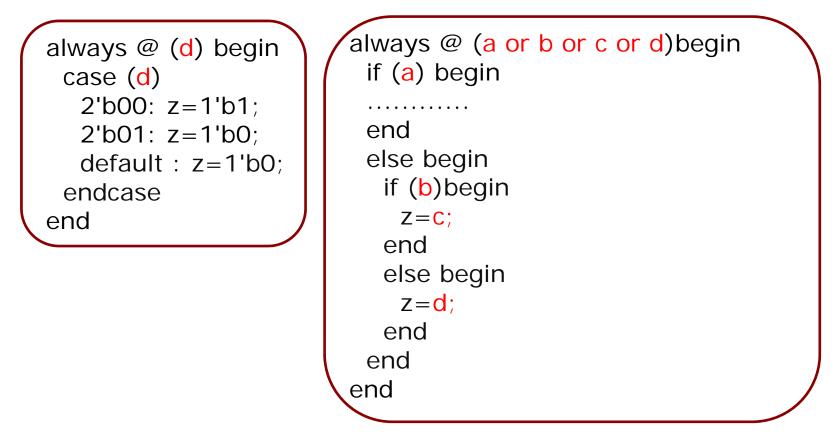

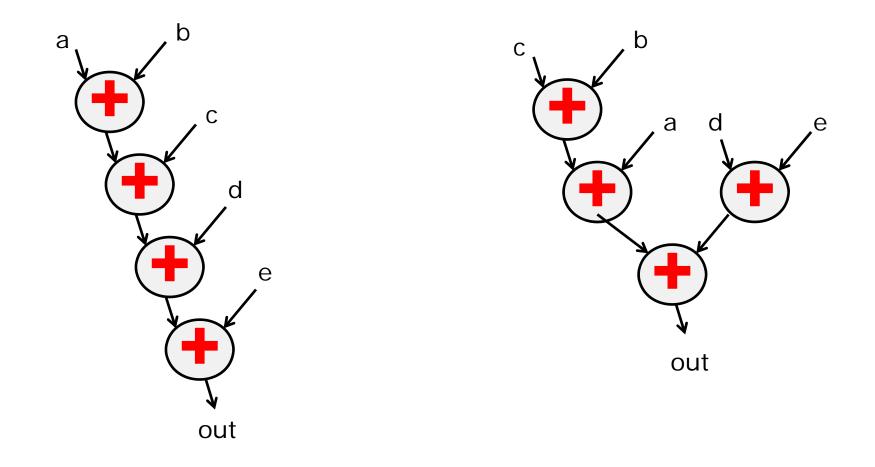

## Write Efficient HDL Code

- Use parentheses control complex structure of a design

- Resource Sharing

- □ Scalable design and propagate constant value

- Use operator bit-width efficiently

- Timescale

#### **Use Parentheses Properly**

$\Box$  out=a+b+c+d+e  $\Box$  out=((a+(b+c))+(d+e));

### **Resource Sharing**

Operations can be shared if they lie in the same always blocks

```

Always @ (sel or a or b or c )

begin

if (sel) z=a+b;

else z=a+c;

end

```

## Scalable Design & Constant

parameter cb\_size=8; parameter data\_size=64; parameter address\_size=13;

input clk; input cen; input wen; input oen; input [address\_size=1:0]address; input [data\_size=1:0]data; // output [data\_size=1:0]Q; output ed; output dec; parameter size=8; wire [3:0] a,b,c,d,e;

assign a=size+2; assign b=a+1; assign c=d+e;

#### Constant Increaser Adder

#### **Use Operator Bit-width Efficiently**

```

module fixed_multiplier(a,b,c);

input [8:0] a, b;

output [8:0] c;

reg [15:0] tmp;

reg [8:0] c;

assign tmp = a*b;

assign c = tmp(15,8);

endmodule

```

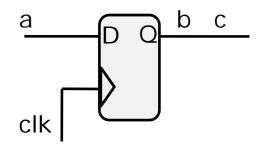

### Timescale

- **timescale**: which declares the time unit and precision.

- timescale <time\_unit> / <time\_precision>

- e.g. : `timescale 1s/1ps, to advance 1 sec, the timewheel scans its queues 10<sup>12</sup> times versus a `timescale 1s/1ms, where it only scans the queues 10<sup>3</sup> times.

- □ The time\_precision must be at least as precise as the time\_unit.

- □ Keep precision as close in scale to the time units as is practical.

- □ If not specified, the simulator may assign a default timescale unit.

- □ The smallest precision of all the timescale directive determines the "simulation time unit" of the simulation.

## **Omit for Synthesis**

- Omit the Wait for XX ns Statement

- Do not use "#XX;"

- Omit the ...After XX ns or Delay Statement

- Do not use "assign #XX Q=0;"

- Omit initial values

- Do not use "initial sum = 1'b0;"

# Non-Synthesizable Style

- Either non-synthesizable or incorrect after synthesis

- □ **initial** block is forbidden (non-synthesizable)

- Multiple assignments (multiple driving sources)

- Mixed blocking and non-blocking assignment

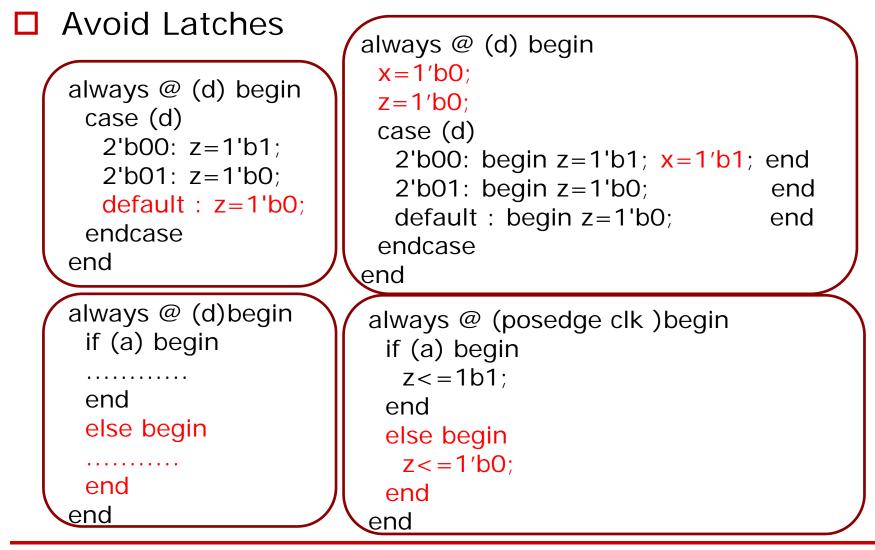

# Summary

- No initial in the RTL code

- Avoid unnecessary latches

- Avoid combinational feedback

- For sequential blocks, use non-blocking statement

- For combinational blocks, use blocking statements

#### Lab 1-2 RTL Simulation

### Tools

#### Simulators

- Verilog-XL, NC-Verilog, Altera Quartus, ModelSim and etc.

- Synthesizers

- Design vision, Ambit, and etc.

- Debugger and verification tools

- Debussy, nWave, nLint, and etc.

- nLint can check the correctness of your code's syntax

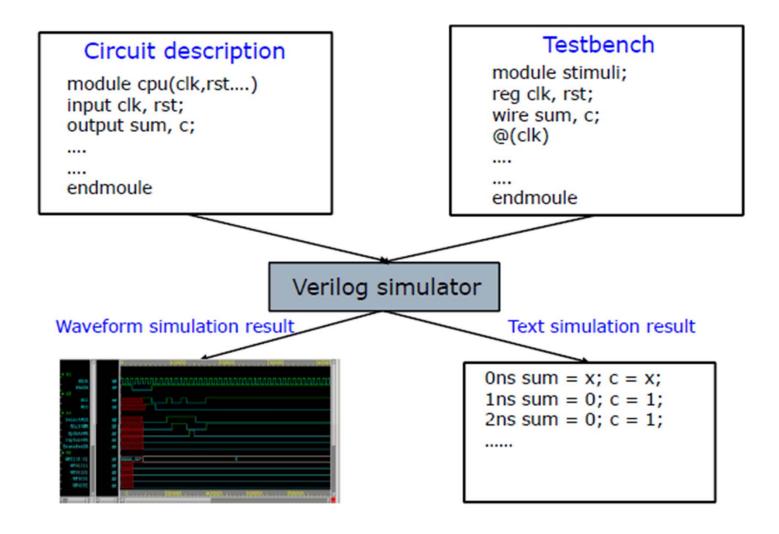

## **Verilog Simulator**

# Run Verilog Simulation(1/2)

#### Method 1:

- unix% verilog alu.v t\_alu.v

- unix% <u>ncverilog +access+r alu.v t\_alu.v</u>

- Method 2:

- Using additional file alu.f

alu.v

t\_alu.v

- unix% verilog -f alu.f

- unix% <u>ncverilog +access+r -f alu.f</u>

- Method 3:

- Using additional description `include "module\_file"

## Run Verilog Simulation(2/2)

Compiling source file "bist\_std1500\_1024x32.v" Highest level modules: bist\_std1500

0 simulation events (use +profile or +listcount CPU time: 0.0 secs to compile + 0.0 secs to lin End of Tool: VERILOG-XL 06.10.001-p N Compiling source file "bist\_std1500\_1024x32.v" Error! syntax error "bist\_std1500\_1024x32.v", 228: 4<-1 error End of Tool: VERILOG-XL \_ 06.10.001-p N

No syntax error

1 Syntax error!

Compare this with your design

module testfixture; •Declare signals •Instantiate modules •Applying stimulus •Monitor signals endmodule

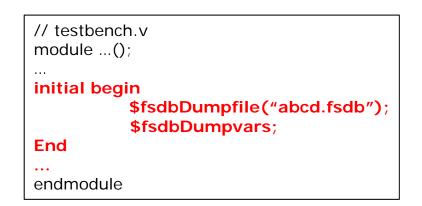

### **FSDB** File

- Waveform file format

- Add commands in testbench

### **Example of Testbench**

```

//t alu.v

/* This is testbench of sample code.

The function is ALU.

*/

module test_ALU;

reg [7:0] A,B;

reg[2:0]SEL;

//alu.v

wire[7:0] OUT;

/* This is sample code.

ALU UO(.a(A),.b(B),.sel(SEL),.out(OUT));

The function is ALU.

always \#5 B = -B;

*/

initial

module ALU(a,b,sel,out);

begin

input [7:0] a,b; //Data in

A=0; B=0; SEL=0;

output[7:0]out; //Data out

#10 A=0; SEL=1;

input [2:0]sel; //Control select

#10 SEL=0;

. . . . .

#10 SEL=1:

reg [7:0]out;

$finish;

#10

wire ...

end

...

initial begin

always@(...)begin

$fsdbDumpfile("ALU.fsdb");

$fsdbDumpvars;

...

end

end

endmodule

. . .

endmodule

```

Advanced Reliable Systems (ARES) Lab.

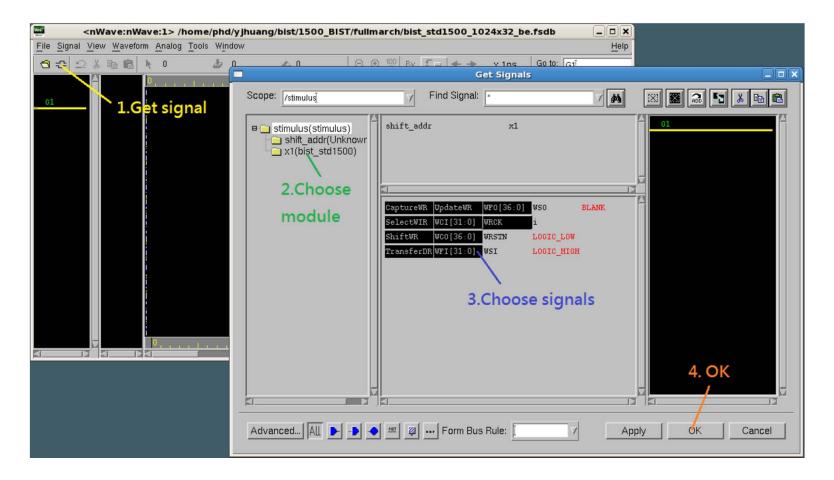

### **Debussy – Getting Start**

#### □ Using nWave or Debussy

unix% nWave&

#### unix% debussy&

|                              | <nwave:nwave:1> No File Opened</nwave:nwave:1>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                      |

|------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| File Signal View Waveform Ar | nalog Tools Window Help                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                      |

| 1 2 3 B B N                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                      |

|                              | Open Dump File                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | _ = ×                |

| ∖<br>File → Open             | File Name                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Delete<br>Delete All |

|                              | /home/phd/yjhuang/bist/1500_BIST/fullmarch     Image: CWmarch       Image: CWmarch     Image: CWmarch       Image: CWmarc | Add                  |

|                              | # marchc         # nLintDB         # nLintDg         # nLintLog         # nLintLog         # nLintLog         # nVaveLog         # pure_logic         # pure_logic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Filter:              |

|                              | Use Signal Grouping Rule File: Browse.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ок                   |

|                              | Open File by Time Range     OP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Cancel               |

## **Get Signals**

#### □ Select "Signal" -> "Get Signal"

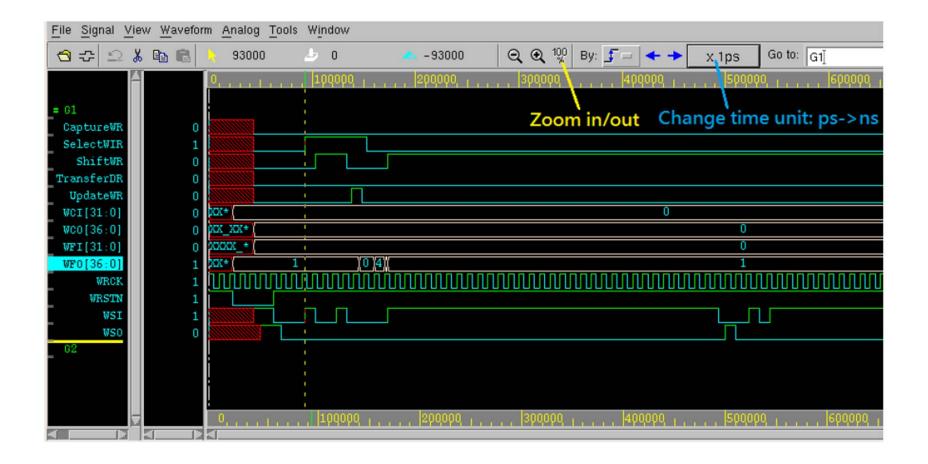

#### **Observe Waveform**

## **Change Radix**

|                                       | $\frown$                            |                                                                                                                 |

|---------------------------------------|-------------------------------------|-----------------------------------------------------------------------------------------------------------------|

| <u>File</u> <u>Signal</u> <u>View</u> | Waveform Analog Tools Window        |                                                                                                                 |

| 3 ↔ 2 % (                             | Auto Update                         | 🔺 -93000 🔍 🔍 🔍 By: 🖵 🗕 🗲 🔶 x 1ps 🛛 Go to: Gīj                                                                   |

|                                       | Spacing                             | ,  zpappa, , , , , ,  zpappa, , , , , ,  4pappa, , , , , ,  spappa, , , , , ,  et                               |

| = 61                                  | Height                              |                                                                                                                 |

| CaptureWR                             | CelonPattern c                      |                                                                                                                 |

| SelectWIR                             | Signal Value <u>R</u> adix          |                                                                                                                 |

| ShiftWR                               | Signal Value Notation               | Binary                                                                                                          |

| TransferDR                            | Analog <u>W</u> aveform             | Octal                                                                                                           |

| UpdateWR                              | Digital Waveform                    | Hexadecimal                                                                                                     |

| WCI[31:0]                             | Bus Invert                          | Decimal 0                                                                                                       |

| WC0[36:0]                             | Bus Reverse                         | ASCII 0                                                                                                         |

| WFI[31:0]<br>WF0[36:0]                | Expand/Shork Properly Signal        |                                                                                                                 |

| WRCK                                  | Ezpand/Shonk Transaction Signal     | IEEE - 754 Floaling Point         1           Add Allos form File         1000000000000000000000000000000000000 |

| WRSTN                                 | Ellier Transaction .                | Add Alias from File                                                                                             |

| WSI                                   | <u>G</u> o To                       | Add Alias from Program                                                                                          |

| WSO                                   | Set Search <u>V</u> alue            | Edit Alias                                                                                                      |

| - <sup>G2</sup>                       | Set Search Constraint               |                                                                                                                 |

|                                       | Snap Cursor to Transitions s        |                                                                                                                 |

|                                       | Fix Cursor/Marker Delta Time 🗙      |                                                                                                                 |

|                                       | Keep Marker at Transaction End Time | ,  zpoopo _ , , , ,  zpoopo _ , , , ,  4poopo _ , , , ,  spoopo _ , , , ,  ep                                   |

|                                       | Keep Cursor at Center y             |                                                                                                                 |

|                                       | Waveform Time                       |                                                                                                                 |

|                                       | Marker M                            |                                                                                                                 |

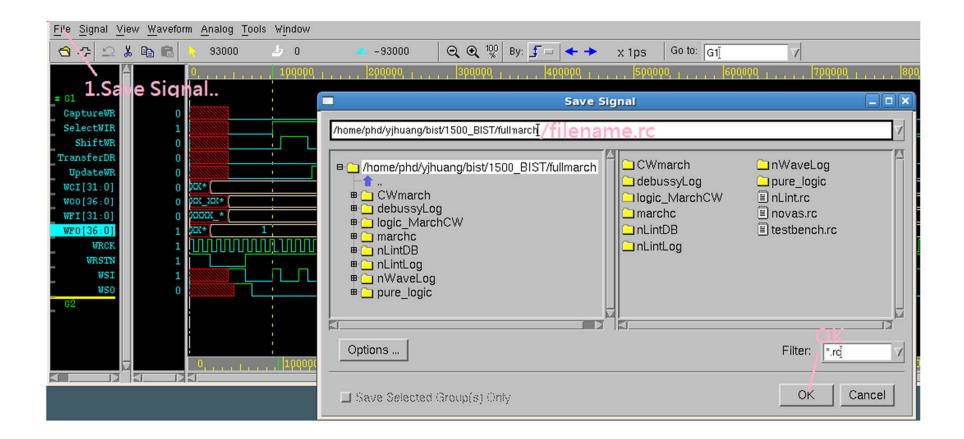

### **Save Waveform**

#### LAB Time